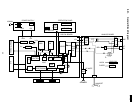

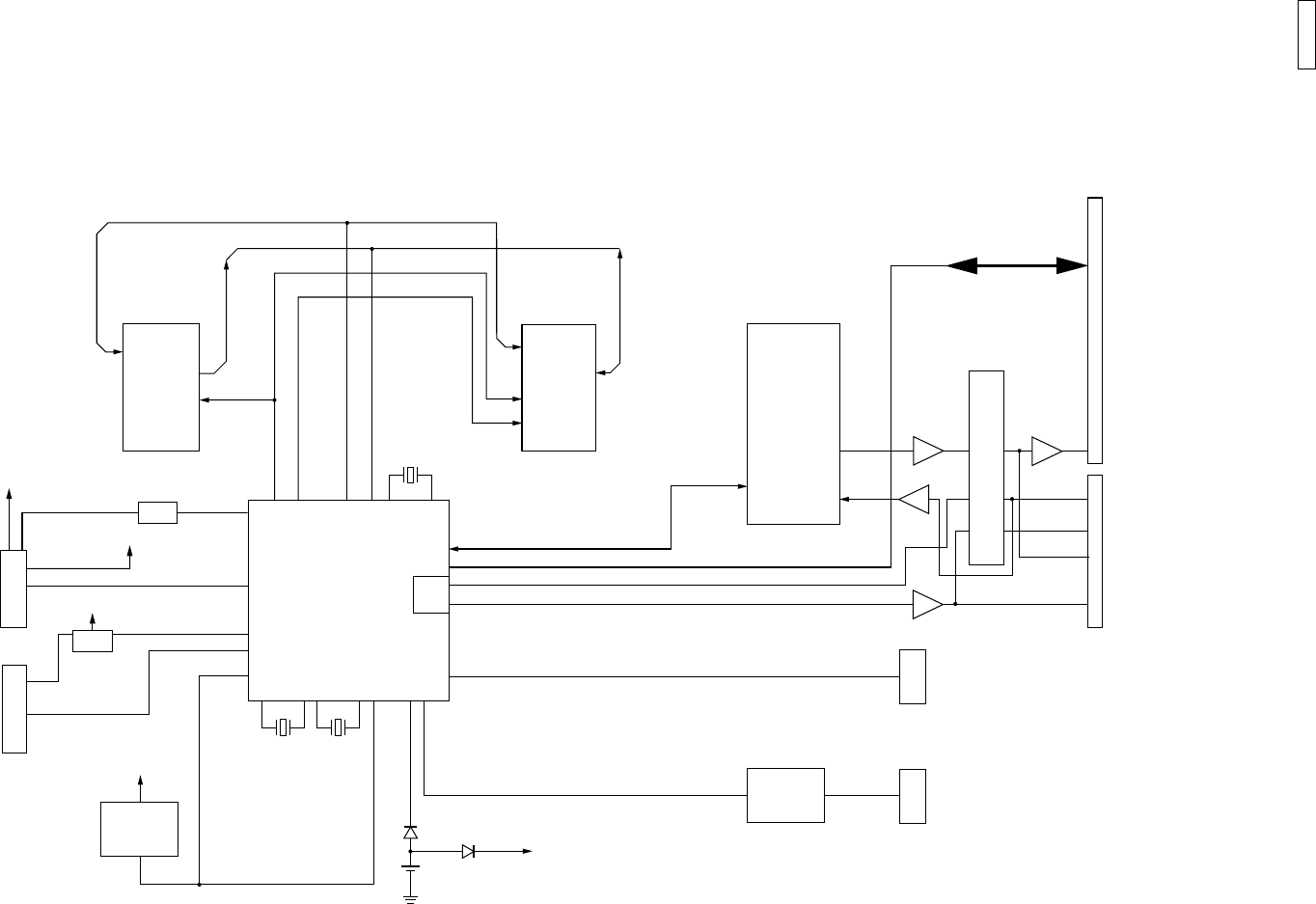

6.3. CONTROL SECTION

6.3.1. BLOCK DIAGRAM

TO

CIS

TO

THERMAL HEAD

CLK, SIG

STBI-2,THLAT

THCLK,THDAT

5V

(IC4)

RESET

BACK UP

ROM (IC2)

A0-17

D0-7

RD

KSTART,KLATCH,KSCLK,KTXD,KRXD,KIN0,KIN1,KIN2,KIN3

RS,E

VOL

HEAD-CTL

XWDERR

RD

WR

XRESETI

A0-17

D0-7

CIS-CTL

LED ON

ASIC

IC1

32.768KHz

20.736MHz

24MHz

T0,T2~T5

(IC7)

MOTOR

DRIVER

TO

MOTOR

TO

OPE PANEL

RX

SP

H/S RX

H/S TX

TX

RXIN

TXOUT

ANALOG FRONT END (IC5)

ANALOG SW

(IC6)

TO ANALOG

TO ANALOG

SRAM (IC3)

A0-17

D0-7

RD

WR

IC7

+5V

+24V

Q13

24V

TH ON

I/O

ANALOG PORT CONTROL

TO SRAM (IC3)

100

KX-FT21RS