1 2 3 4 5 6

A

B

C

D

654321

D

C

B

A

Title

Number RevisionSize

B

Date: 10-Oct-2002 Sheet of

File: D:\wzw\Myproj\isp1301\eva_kit\eva board\pcb\02226-1.ddbDrawn By:

ADR

1

SDA

2

SCL

3

RESET_N

4

INT_N

5

SPEED

6

VOUT33

7

SUSPEND

8

OE_TP_INT_N

9

VM

10

VP

11

RCV

12

SE0_VM

13

DAT_VP

14

D-

15

D+

16

AGND

17

ID

18

VBUS

19

VBAT

20

C1

21

C2

22

CGND

23

VIO

24

GND

25

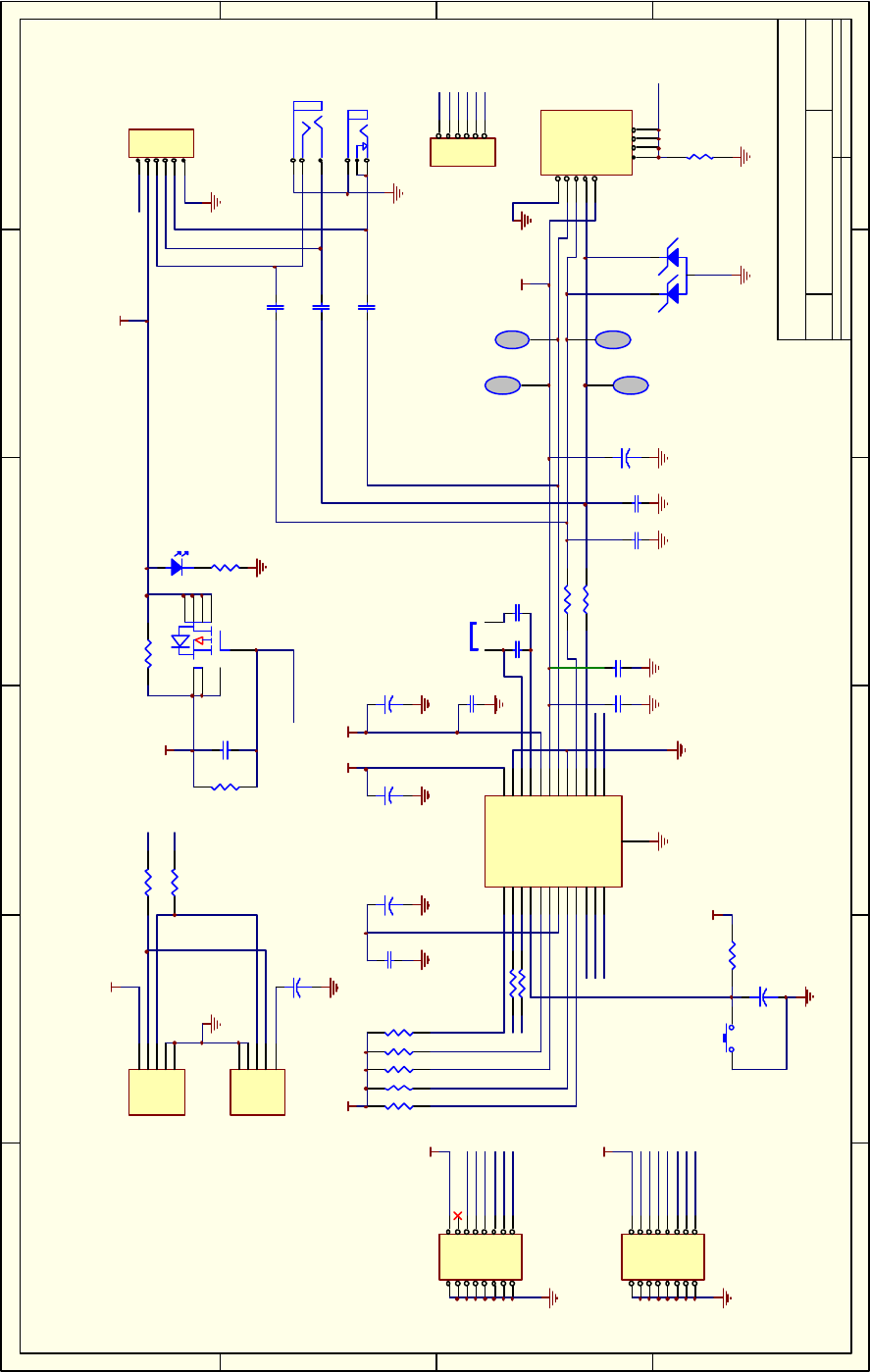

U1

ISP1301

R13

33R%1

R14

33R%1

VBUS

1

D-

2

D+

3

ID

4

GND

5

SHIELD

6

SHIELD

7

SHIELD

8

SHIELD

9

J9

USB mini-AB receptacle

C11

0.1uF

C10

0.1uF

C1

0.1uF

C14

22pF

C15

22pF

C12

28nF

C13

120nF

1

2

JP1

JUMPER

SW1

SW-PB

+

C6

4.7uF16V

+

C4

4.7uF16V

+

C3

4.7uF16V

ISP1301 EVALUATION BOARD

A

+ C16

4.7uF16V

R6

10K

R7

10K

R8

10K

R9

10K

R10

10K

VIO VBATVIO

R15

10K

+ C17

1uF

VIO

PAD

1

TP1

VBUS

PAD

1

TP3

ID

PAD

1

TP2

D-

PAD

1

TP4

D+

R11 100R

R12 100R

C7

220nF

C8

220nF

C9

220nF

R16

100R

A

1

B

2

C

3

J6

PHONEJACK STEREO(SPK LINE IN)

J7

PHONEJACK(MIC LINE OUT)

VBUS

D-

D+

ID

1

4

7

8

5

62

3

Q1 PHP125

R4

0

R3

10K

C5

0.1uF

CHRG_EN

3

2

1

D1

STZ5.6N

VBUS

1

D-

2

D+

3

GND

4

CHASSIS

5

J1

USB A-RECEPTACLE

VBUS

1

D-

2

D+

3

GND

4

CHASSIS

5

J4

USB B-RECEPTACLE

H_VBUS

D-

D+

+5V

+

C2

10uF16V

R1

0

R2

0

ADR

SDA

SCL

RESET_N

INT_N

SPEED

SUSPEND

OE_TP_INT_N

VM

VP

RCV SE0_VM

DAT_VP

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

J3

HEADER 8X2

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

J8

HEADER 8X2

ADR

SDA

SCL

RESET_N

INT_N

SPEED

SUSPEND

OE_TP_INT_N

VM

VP

RCV

SE0_VM

DAT_VP

VIO

VBAT

ISP1301 PORT V1.0

1/2

LOUT

LIN_L

LIN_R

VBUS

D-

D+

ID

GND

SHIELD

1

2

3

4

5

6

J5

HEADER 6

SHIELD

LED1

5.0V

R5

4.7K

NOT INSTALL

LOUT

LIN_L

LIN_R

GND

5VOUT

VBUS

VBUS

5VOUT

1

2

3

4

5

6

J2

HEADER 6

GNDD_VBUS

C50

0.1uF