Philips Semiconductors ISP1301 USB OTG Transceiver Eval Kit User’s Guide

UM10028_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

User’s Guide Rev. 1.0—February 2003 3 of 18

CONTENTS

1. INTRODUCTION ...............................................................................................................................5

2. SYSTEM REQUIREMENTS................................................................................................................ 5

3. CONFIGURATIONS AND SETTINGS............................................................................................6

3.1. POWER REQUIREMENTS......................................................................................................................................................6

3.2. I

2

C MASTER SELECTION ......................................................................................................................................................6

3.3. USB INTERFACE ..................................................................................................................................................................7

3.4. AUDIO INTERFACE ..............................................................................................................................................................7

3.5. RESET ...................................................................................................................................................................................7

4. LOCATION OF MAJOR COMPONENTS .......................................................................................7

5. TEST PROGRAM 1301.EXE ..............................................................................................................8

5.1. INTRODUCTION..................................................................................................................................................................8

5.2. RUNNING THE TEST PROGRAM..........................................................................................................................................9

5.3. USING MENUS......................................................................................................................................................................9

5.3.1. Choose I2C slave address for ISP1301..................................................................................................................................9

5.3.2. Reset all registers .........................................................................................................................................................................9

5.3.3. List all registers .......................................................................................................................................................................... 10

5.3.4. Read/Write register .................................................................................................................................................................. 10

5.3.5. Select Mode of Operation....................................................................................................................................................... 11

5.3.6. Enable/Disable charge-pump................................................................................................................................................. 11

6. HARDWARE DESCRIPTION..........................................................................................................12

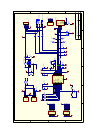

6.1. BLOCK DIAGRAM ..............................................................................................................................................................12

6.2. FUNCTIONAL DESCRIPTION.............................................................................................................................................12

6.2.1. PCF8584 I

2

C-bus controller ....................................................................................................................................................12

6.2.2. PC parallel to I

2

C converter .................................................................................................................................................... 12

6.2.3. HC, DC and OTG core logic interface connector............................................................................................................. 12

6.2.4. Power manager.......................................................................................................................................................................... 13

6.2.5. Audio interface........................................................................................................................................................................... 13

7. CONNECTOR PIN INFORMATION..............................................................................................13

7.1. DB-25 PC PARALLEL PORT CONNECTOR (J10) PIN ASSIGNMENT...............................................................................13

7.2. 8-BIT MICROPROCESSOR INTERFACE 20 X 2 HEADER (J13) PIN ASSIGNMENT.............................................................13

7.3. USB OTG CONTROLLER INTERFACE 8 X 2 HEADER (J8 AND J3) PIN ASSIGNMENT.................................................13

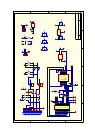

8. SCHEMATICS OF THE EVALUATION BOARD .........................................................................14

9. BILL OF MATERIALS.......................................................................................................................17

10. REFERENCES ....................................................................................................................................18