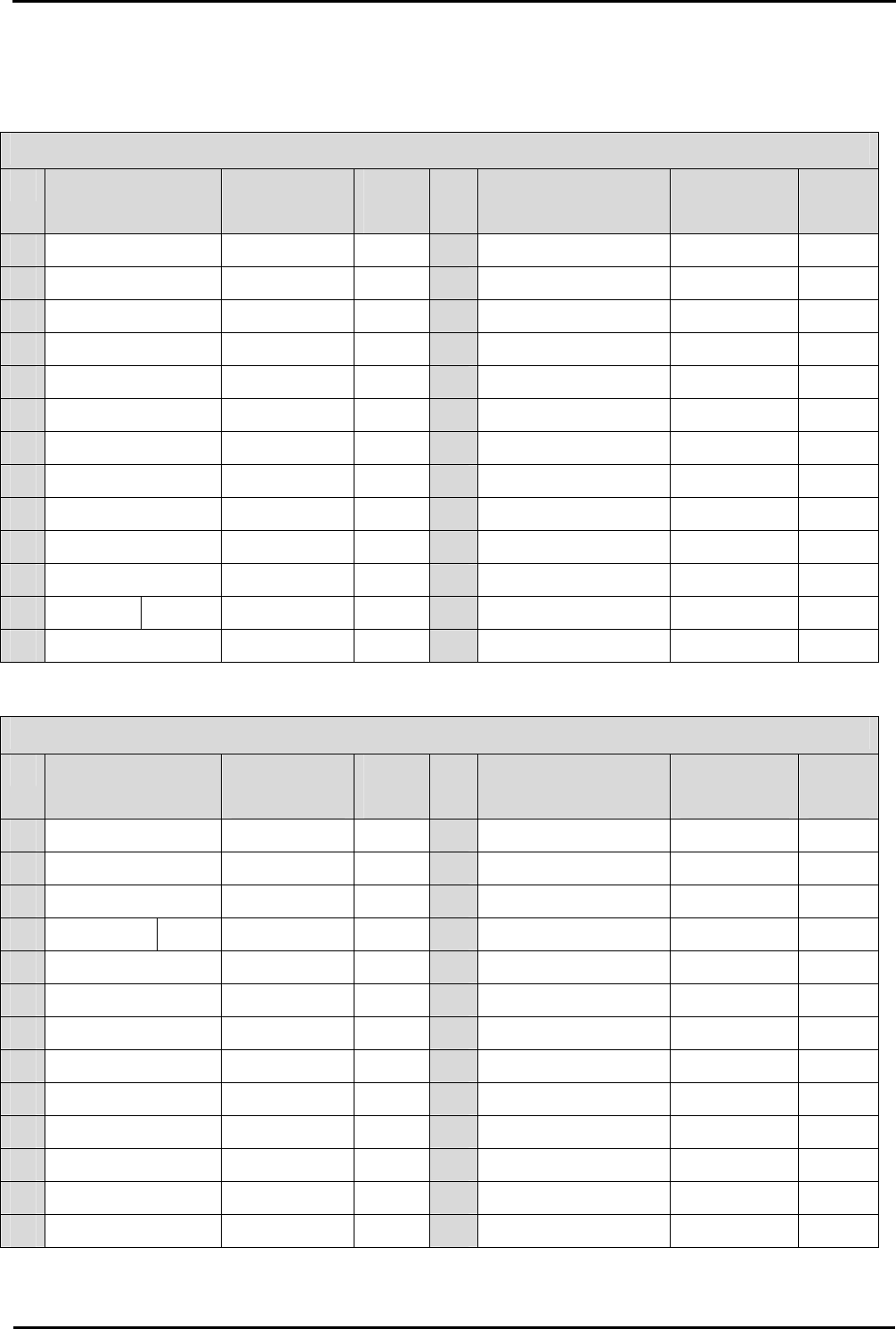

9.2. Application Headers

Table 9-5 and belowTable 9-9 show the standard application header connections.

JA1

Pin Generic Header Name CPU board

Signal Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 Regulated Supply (5V) --- --- 2 Regulated Supply 1 (Gnd) --- ---

3 Regulated Supply (3V3) --- --- 4 Regulated Supply 2 (Gnd) --- ---

5 Analog Supply AVcc* 51 6 Analog Supply AVss 43

7 Analog Reference AVref* 50 8 ADTRG ADTRG_IRQ3n* 83

9 AD0 AN0* 49 10 AD1 AN1 48

11 AD2 AN2 47 12 AD3 AN3 46

13 DAC0 DAC0* 45 14 DAC1 DA1* 44

15 IOPort IO0* 20 16 IOPort IO1* 21

17 IOPort IO2* 23 18 IOPort IO3* 25

19 IOPort IO4* 26 20 IOPort IO5* 27

21 IOPort IO6* 28 22 IOPort IO7* 29

23 Open drain IRQ3n ADTRG_IRQ3n* 83 24 IIC_EX --- ---

25 IIC_SDA --- --- 26 IIC_SCL --- ---

Table 9-5: JA1 Standard Generic Header

JA2

Pin Generic Header Name CPU board

Signal Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 Open drain RESn 72 2 External Clock Input CON_EXTAL* 76

3 Open drain NMI 70 4 Regulated Supply (Vss) --- ---

5 Open drain output --- --- 6 Serial Port TxD0* 88

7 Open drain WUP IRQ0 39 8 Serial Port RxD0* 89

9 Open drain IRQ2 87 10 Serial Port SCK0* 90

11 Up/down UD 99 12 Serial Port Handshake --- ---

13 Motor control Up* 35 14 Motor control Un* 36

15 Motor control Vp* 37 16 Motor control Vn 38

17 Motor control Wp* 40 18 Motor control Wn 41

19 Output TMR0 98 20 Output TMR1 97

21 Input TRIGa 100 22 Input TRIGb 42

23 Open drain ADTRG_IRQ3n* 83 24 Tristate Control TRISTn 96

25 Reserved ---

---

26 Reserved ---

---

Table 9-6: JA2 Standard Generic Header

27