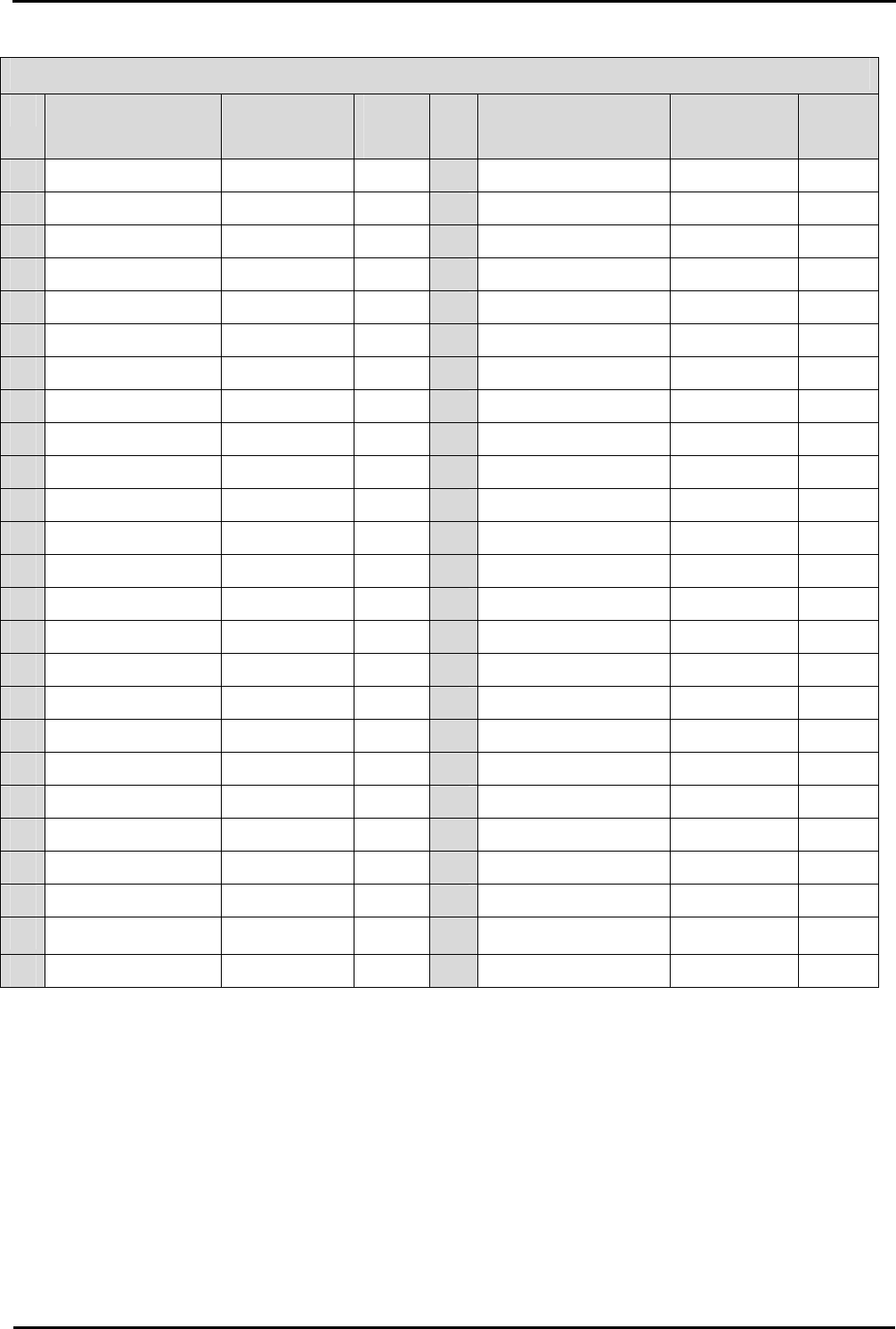

JA3

Pin Generic Header Name CPU board

Signal Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 Address Bus A0 11 2 Address Bus A1 13

3 Address Bus A2 14 4 Address Bus A3 15

5 Address Bus A4 16 6 Address Bus A5 17

7 Address Bus A6 18 8 Address Bus A7 19

9 Address Bus A8* 20 10 Address Bus A9* 21

11 Address Bus A10* 23 12 Address Bus A11* 25

13 Address Bus A12* 26 14 Address Bus A13* 27

15 Address Bus A14* 28 16 Address Bus A15* 29

17 Data Bus D0_DLCDRS 111 18 Data Bus D1_DLCDE 113

19 Data Bus D2 115 20 Data Bus D3 116

21 Data Bus D4_DLCD4 117 22 Data Bus D5_DLCD5 118

23 Data Bus D6_DLCD6 119 24 Data Bus D7_DLCD7 120

25 Read/Write Control RDn 80 26 Read/Write Control LWRn* 83

27 Memory Select CS0n 105 28 Memory Select CS1n 104

29 Data Bus D8 2 30 Data Bus D9 3

31 Data Bus D10 4 32 Data Bus D11 5

33 Data Bus D12 6 34 Data Bus D13 7

35 Data Bus D14 8 36 Data Bus D15 9

37 Address Bus A16* 30 38 Address Bus A17* 31

39 Address Bus A18* 32 40 Address Bus A19* 33

41 Address Bus A20* 35 42 Address Bus A21* 36

43 Address Bus A22* 37 44 External Device Clock PHI 78

45 Memory Select CS2n 103 46 Bus Control ASn 79

47

Data Bus Strobe HWRn 81

48

Data Bus Strobe LWRn* 83

49 Reserved 50 Reserved

Table 9-7: JA3 Expansion bus Header

28