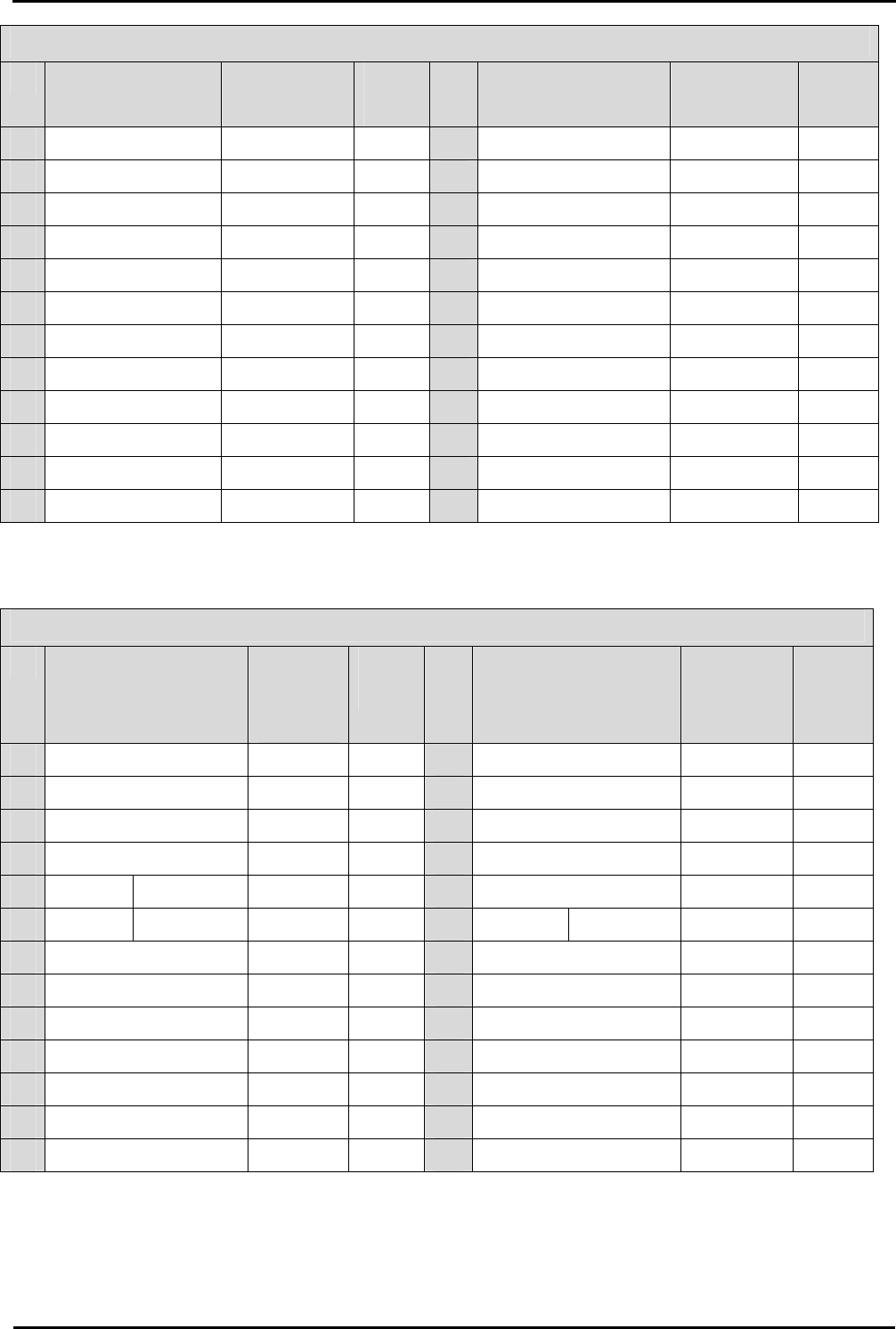

JA5

Pin Generic Header Name CPU board

Signal Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 AD4 AN14* 45 2 AD5 AN15* 44

3 AD6 --- --- 4 AD7 --- ---

5 CAN1TX --- --- 6 CAN1RX --- ---

7 CAN2TX --- --- 8 CAN2RX --- ---

9 AD8 --- --- 10 AD9 --- ---

11 AD10 --- --- 12 AD11 --- ---

13 TIOC0A --- --- 14 TIOC0B --- ---

15 TIOC0C --- --- 16 M2_TRISTn --- ---

17 TCLKC --- --- 18 TCLKD --- ---

19 M2_Up --- --- 20 M2_Un --- ---

21 M2_Vp --- --- 22 M2_Vn --- ---

23 M2_Wp --- --- 24 M2_Wn --- ---

Table 9-8: JA5 Optional Generic Header

JA6

Pin Generic Header Name CPU board

Signal

Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 DMA --- --- 2 DMA --- ---

3 DMA --- --- 4 Standby (Open drain) STBYn 71

5 Host Serial RS232TX* --- 6 Host Serial RS232RX* ---

7 Serial Port RxD1 92 8 Serial Port TxD1 91

9 Serial Port Synchronous PTTX* 31 10 Serial Port SCK1 93

11 Serial Port Synchronous SCK2* 33 12 Serial Port Synchronous PTRX* 32

13 Reserved 14 Reserved

15 Reserved 16 Reserved

17 Reserved 18 Reserved

19 Reserved 20 Reserved

21 Reserved 22 Reserved

23 Reserved 24 Reserved

25 Reserved 26 Reserved

Table 9-9: JA6 Optional Generic Header

* Marked pins are affected by option links (see 6.6).

29