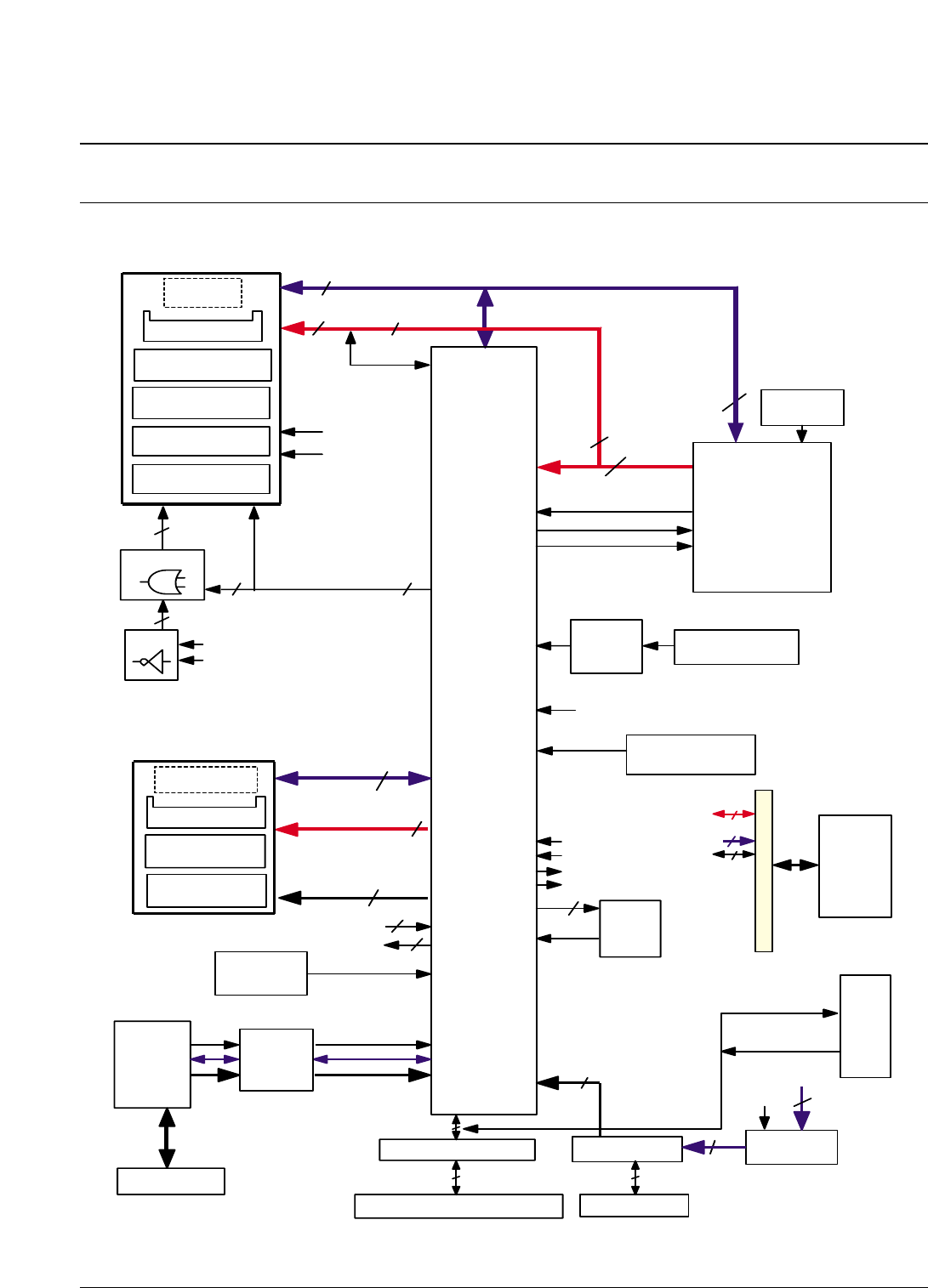

6. Block Diagram

6-1 Video ControllerBlock Diagram

6-1

22

ADDR(0:31)

29LV160

16Mbit Flash Memory

Mask Font ROM

K3P5V1000D-GC,High

ROM

29LV160

16Mbit Flash Memory

Mask Font ROM

K3P5V1000D-GC,Low

DATA(0:31)

32

SPGPi

3

nFSYNC

4

ACK*, BUSY,

SELECT, ERROR,

FAULT*

SELIN*

STROBE*

AUTOFD*

INI*

PD(0: 7 )

EIRQ(0:3)*

4

nIOCS(0:5)*

6

CPU

POWER PC

PPC603ei

166MHz

32

Regulator

2.7V

RCS(0:3)

4

nWAIT

nWR

INT*

nRD

2

Centronics

Connector

PA N E L 8P in

3

Engine I/F Connector

38

Engine Controller B'd

100PIN DIMM

OP Panel

74HCT273

D Flip-Flop

DATA(0:7)

8

IOCS0

6

0

P

i

n

N

e

t

w

o

r

k

C

o

n

n

e

c

t

o

r

OPTION

Network

Card

ADDR(2:18)

DATA(16:31)

nWAIT

nRD

nWR

TT1

BRDIN*

IOCS1

IOCS2

EIR Q 2

Computer

TS*, TT1,nTSBT,TSIZ(0:2)

SYSCLK

nTA,RST*,INT*,nTS,n BG

21

ADDR(2:22)

A20

System clock

11.1MHz(OSC)

FS781

Frequency

Scaling EMI

Attenuator

RESET*

C7733

Supply Voltage

Supervi sor

DATA(0:31)

RD_FL ASH*

WR_FLASH1,2,3

Video-Clock

61.23307M Hz

VCLK*

74F32

nWR

F_W R_E

74F04

32

Memory Data Bus

11

MemoryAddressBus

14

SDRA M_CAS,SDRA M_RA S,

BA0*,BA1*,SDRAM_WE*,

SDRAM_CS(0:1),SDQM(0:3),

SD_CLK(1:2) ,CL KE

64Mbit SDRAM

K4S641632C

SDRA M

64Mbit SDRAM

K4S641632C

DRAMA(0:11)

DRAMD(0:31)

100PIN DIMM

74ACT245

Transceiver

93C66

4Mbit

Se ri al

EEPROM

3

5

THV_PWM *,MHV_PWM*,

DEV_PWM,THVEN*,

LD ON*, PMOT O R* ,

LSUCLK,nVIDEO*

To

HVPS

&

LSU

LREADY*,LSYNC*

32