AN93

Rev. 1.3 25

2.2.4.1. Hardware Interface Register 0

Hardware Interface Register 0 (HIR0) is the eight-bit wide read/write location where modem data and commands

are exchanged with the host. Writing a byte to the HIR0 adds that byte to the modem’s transmit FIFO (AT

command buffer in command mode or data transmission in data mode). If data are available (modem data in data

mode or command responses, such as OK, in command mode), reading from the HIR0 fetches data from the

modem’s receive FIFO. The maximum burst data rate is approximately 350 kbps (45 kBps).

2.2.4.2. Hardware Interface Register 1

Hardware Interface Register 1 (HIR1) contains various status and control flags for use by the host to perform data

flow control, to escape to command mode and to query various interrupt conditions. The HIR1 bit map is described

in Table 22. This register is reset to 0x63.

Bit 7 (RXF) is a read/write bit that gives the status of the 12-byte deep receive FIFO. If RXF = 0, the receive FIFO

contains less than 10 bytes. If RXF = 1, the receive FIFO contains more than 9 bytes and is full or almost full.

Writing RXF = 0 clears the interrupt.

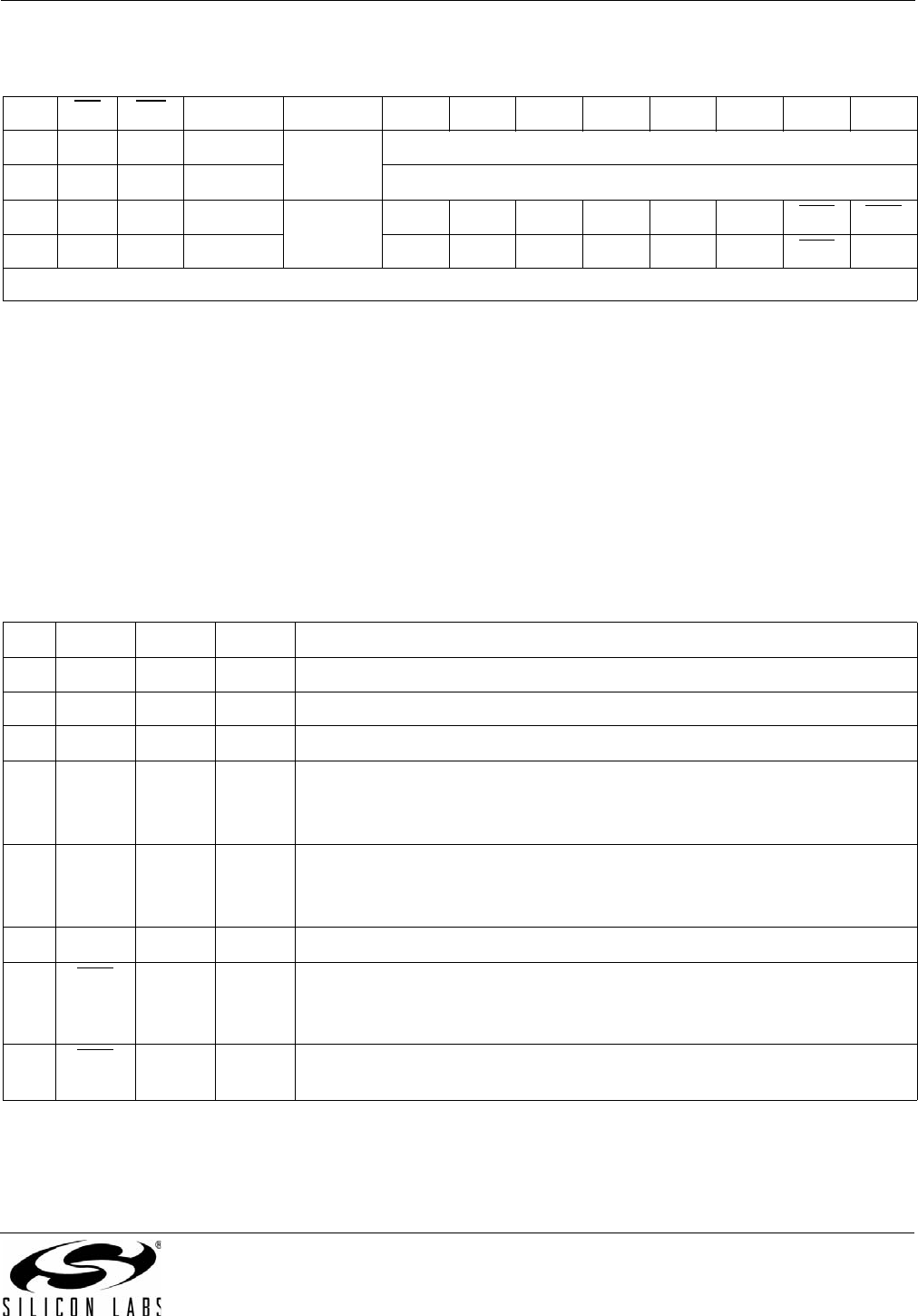

Table 21. Hardware Interface Register Bit Map

A0 RD WR Action Register D7 D6 D5 D4 D3 D2 D1 D0

0 0 1 Read HIR0 Modem data or command from receive FIFO

0 1 0 Write Modem data or command to transmit FIFO

1 0 1 Read HIR1 RXF TXE REM INTM INT ESC RTS

CTS

1 1 0 Write RXF TXE *Note INTM *Note ESC RTS n/a

*Note: REM and INT are read-only bits.

Table 22. Hardware Interface Register 1

Bit Name R/W Reset Function

7RXFR/W 0Receive FIFO Almost Full

6TXER/W 1Transmit FIFO Almost Empty

5REM R 1Receive FIFO Empty

4INTMR/W 0Interrupt Mask

0 = INT pin triggered on rising edge of RXF or TXE only

1 = INT pin triggered on rising edge of RXF, TXE or INT (bit 3 below)

3INT R 0Interrupt

0 = No interrupt

1 = Interrupt triggered

2 ESC R/W 0 Escape

1RTS

R/W 1 Request-to-Send (active low) — Deprecated — for flow control, use the

TXE and REM bits for polling- or interrupt-based communication.

This bit must be written to zero.

0CTS

R1Clear-to-Send (active low) — Deprecated — for flow control, use the TXE

and REM bits for polling- or interrupt-based communication.