10/100 Non-PCI Ethernet Single Chip MAC + PHY

Datasheet

SMSC LAN91C111 REV C 15 Revision 1.91 (08-18-08)

DATASHEET

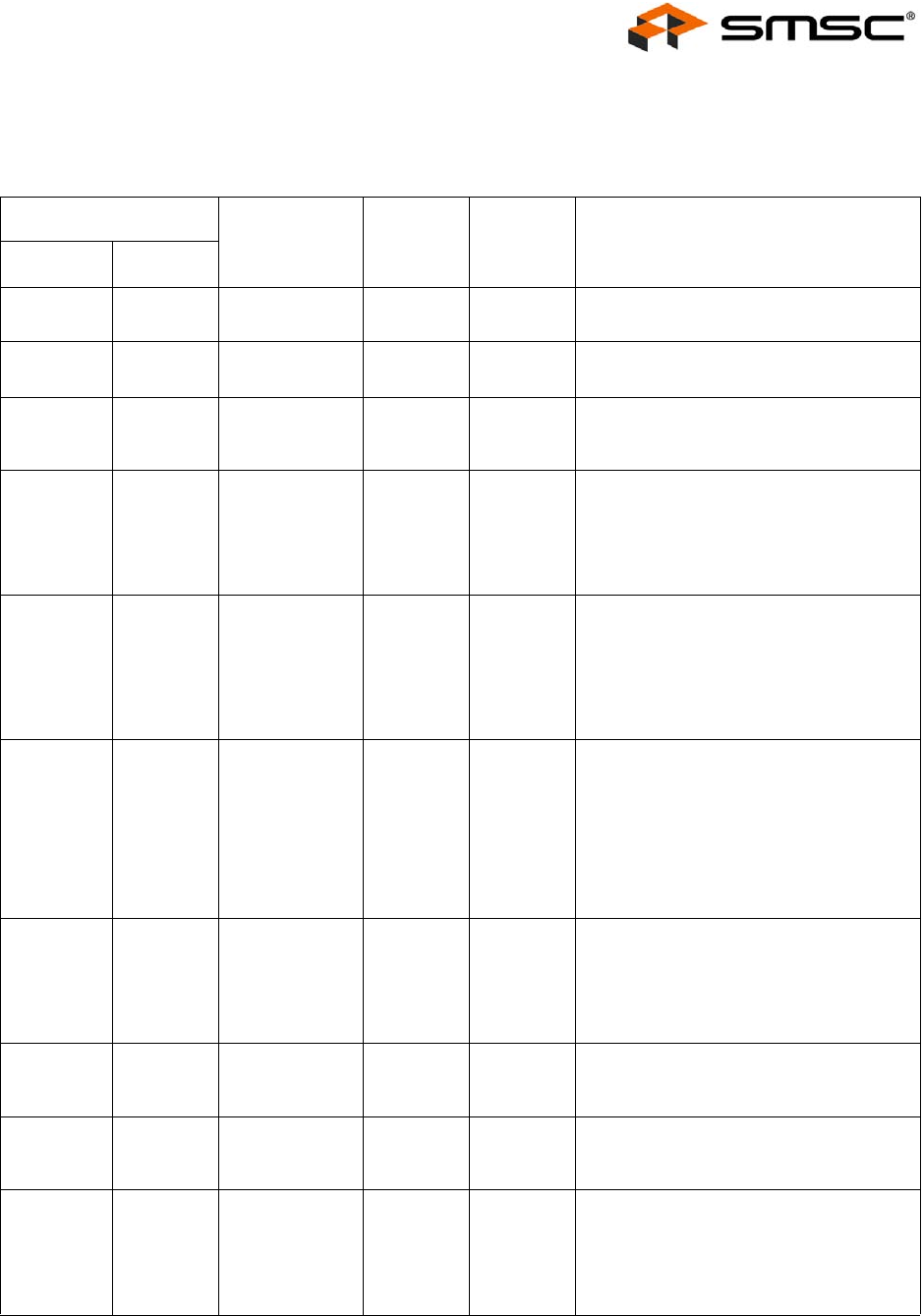

Chapter 5 Description of Pin Functions

PIN NO.

NAME SYMBOL

BUFFER

TYPE

DESCRIPTION

TQFP QFP

81-92 83-94 Address A4-A15 I** Input. Decoded by LAN91C111 to

determine access to its registers.

78-80 80-82 Address A1-A3 I** Input. Used by LAN91C111 for internal

register selection.

41 43 Address Enable AEN I** Input. Used as an address qualifier.

Address decoding is only enabled when

AEN is low.

94-97 96-99 nByte Enable nBE0-

nBE3

I** Input. Used during LAN91C111 register

accesses to determine the width of the

access and the register(s) being

accessed. nBE0-nBE3 are ignored when

nDATACS is low (burst accesses)

because 32 bit transfers are assumed.

107-104,

102-99, 76-

73, 71-68,

66-63, 61-

58, 56-53,

51-48

109-106,

104-101,

78-75, 73-

70, 68-65,

63-60, 58-

55, 53-50

Data Bus D0-D31 I/O24** Bidirectional. 32 bit data bus used to

access the LAN91C111’s internal

registers. Data bus has weak internal

pullups. Supports direct connection to the

system bus without external buffering.

For 16 bit systems, only D0-D15 are

used.

30 32 Reset RESET IS** Input. When this pin is asserted high, the

controller performs an internal system

(MAC & PHY) reset. It programs all the

registers to their default value, the

controller will read the EEPROM device

through the EEPROM interface

(Note 5.1).

This input is not considered active unless

it is active for at least 100ns to filter

narrow glitches.

37 39 nAddress

Strobe

nADS IS** Input. For systems that require address

latching, the rising edge of nADS

indicates the latching moment for A1-A15

and AEN. All LAN91C111 internal

functions of A1-A15, AEN are latched

except for nLDEV decoding.

35 37 nCycle nCYCLE I** Input. This active low signal is used to

control LAN91C111 EISA burst mode

synchronous bus cycles.

36 38 Write/

nRead

W/nR IS** Input. Defines the direction of

synchronous cycles. Write cycles when

high, read cycles when low.

40 42 nVL Bus Access nVLBUS I with

pullup**

Input. When low, the LAN91C111

synchronous bus interface is configured

for VL Bus accesses. Otherwise, the

LAN91C111 is configured for EISA DMA

burst accesses. Does not affect the

asynchronous bus interface.