83

-

507

-

013 Rev. D

65

Refer to Tables 7

-

10 to 7

-

13 for details of the Enable and Event registers.

1.

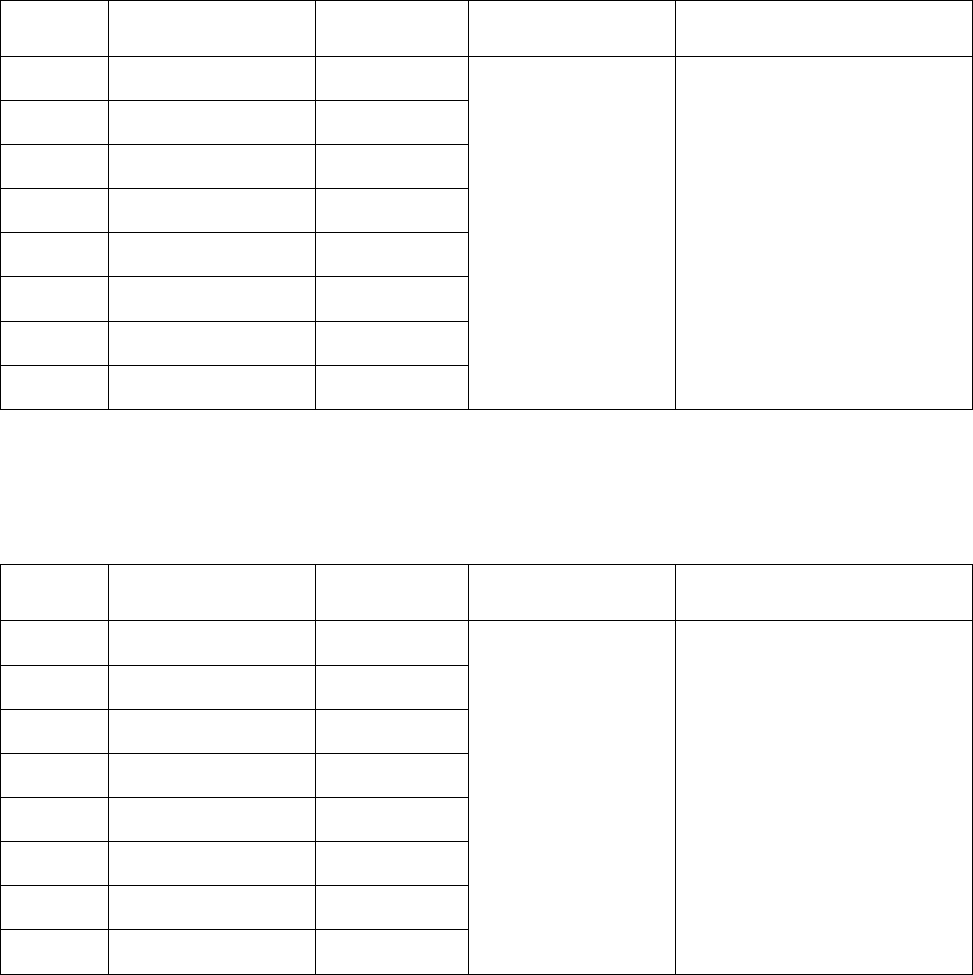

Fault Enable Register

The Fault Enable Register is set to the enable faults SRQs.

Table 7

-

10: Fault Enable Register

BIT

Enable

bit name

Fault symbol

Bit Set condi

tion

Bit reset condition

0 (LSB)

Spare bit

SPARE

1

AC Fail

AC

2

Over Temperature

OTP

3

Foldback

FOLD

4

Over Voltage

OVP

5

Shut Off

SO

6

Output Off

OFF

7(MSB)

Enable

ENA

User command:

“FENA nn” where

nn is hexadecimal

User command: “FENA nn”

where nn is hexadecimal (if

nn=”00”, no fault SRQs will

be generated).

2.

Fault Event Register

The Fault Event will set a bit if a condition occurs and it is Enabled. The register is cleared when

FEVE?, CLS or RST commands are received.

Table 7

-

11: Fault Event Register

BIT

Enable

bit name

Fault symbol

Bit Set condition

Bit reset condition

0 (LSB)

Spare bit

SPARE

1

AC Fail

AC

2

Over Temperature

OTP

3

Foldback

FOLD

4

Over Voltage

OV

P

5

Shut Off

SO

6

Output Off

OFF

7(MSB)

Enable

ENA

Fault condition

occurs and it is

e

n

abled.

The fault can set a

bit, but when the

fault clears the bit

remains set.

Entire Event Re

gister is

cleared when user sends

“FEVE?” command to read

the register.

“CLS” and power

-

up also

clear the Fault Event Regi

s-

ter. (The Fault Event Regi

s-

ter is not cleared by RST)