Adapter Internal Registers

A-34

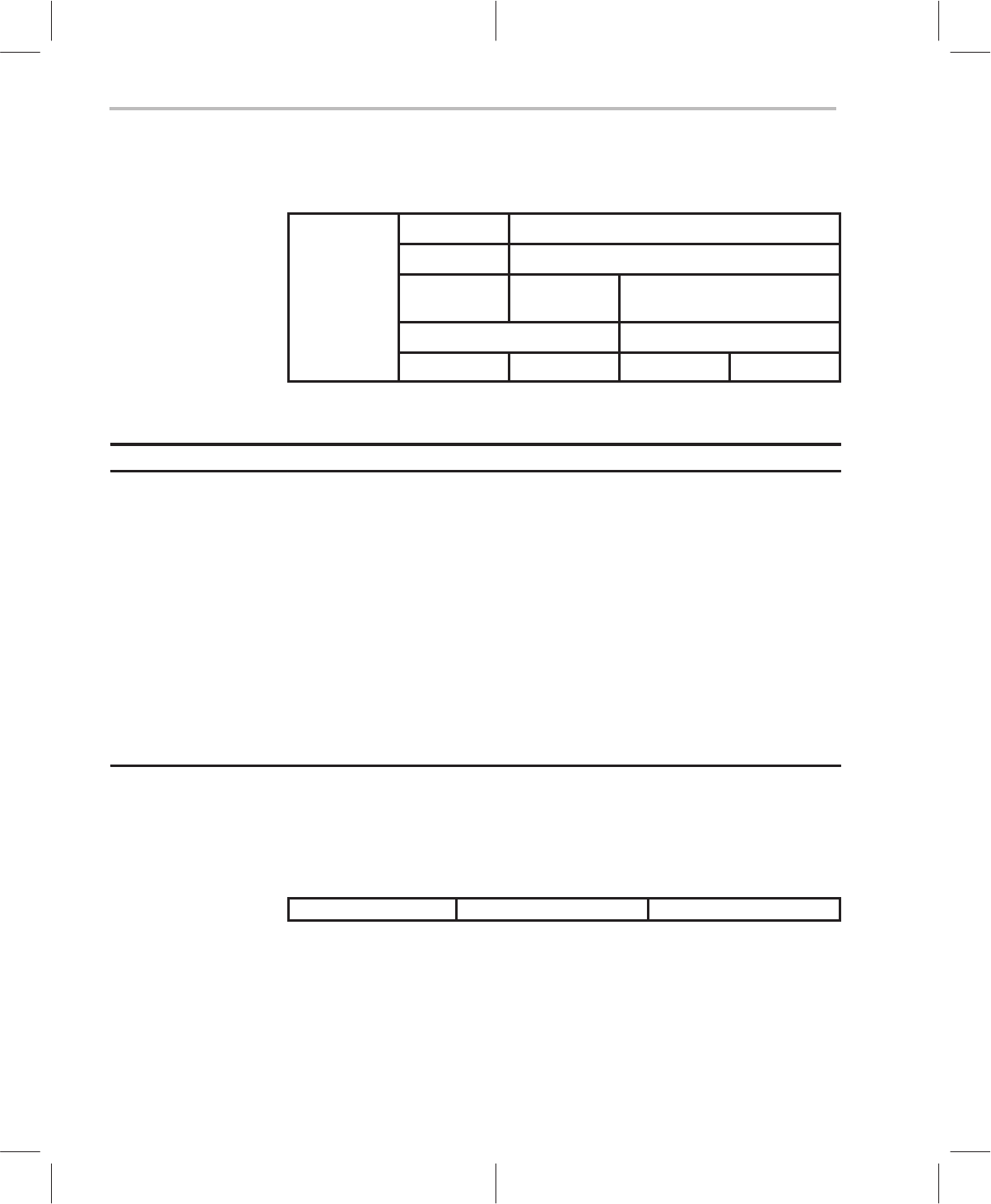

Figure A–7. Demand Priority Error Counters

DIO Address Byte 3 Byte 2 Byte 1 Byte 0

0x30

Rx overrun Good Rx frames

0x34 Tx underrun Good Tx frames

0x38 Code error

frames

CRC error

frames

Deferred Tx

frames

0x3C

0x40

Table A–15. Demand Priority Error Counters

Counter Definition

Good Tx frames are transmitted without errors. This is a 24-bit counter. Good frames are transmitted

more frequently than errored frames.

Tx underrun frames are aborted during transmission, due to frame data not being available (due to host

bus latencies). This is a byte-wide counter.

Good Rx frames are received without errors. This is a 24-bit counter. Good frames are received more

frequently than errored frames.

Rx overrun frames are address-matched and could not be received due to inadequate resources (Rx

FIFO full). This is a byte-wide counter.

CRC error frames are received with CRC errors, but without alignment or coding errors. This is a byte-

wide counter.

Code error frames

are received with alignment (not an even number of nibbles) or code errors (MRXER

signaled from PMI). This is a byte-wide counter.

A.3.11 Adapter Commit Register–Acommit @ 0x40 (DIO) (Byte 3)

The adapter commit register indicates the PCI commit size of the adapter.

Byte 3 31 30 29 28 27 26 25 24

Tx commit level PHY options