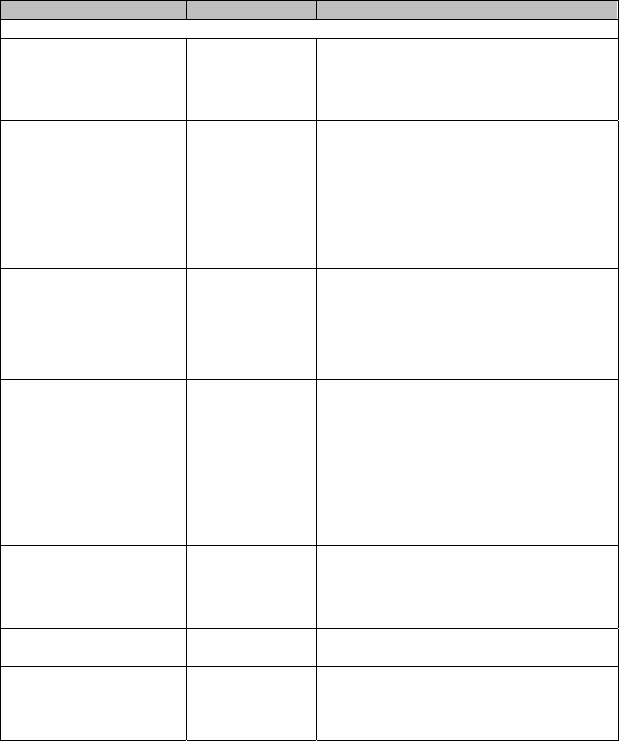

Feature Option Description

NorthBridge Chipset Configuration

CAS Latency (Tcl) Read only

This controls the timing delay (in clock

cycles) before SDRAM starts a read

command after receiving it.

RAS/CAS Delay (Trcd) Read only

When DRAM is refreshed, both rows

and columns are addressed

separately. This setup item allows you

to determine the timing of the transition

from RAS (row address strobe) to CAS

(column address strobe). The less the

clock cycles, the faster the DRAM

performance.

Min Active RAS (Tras) Read only

This setting allows you to select the

number of clock cycles allotted for the

RAS pulse width, according to DRAM

specifications. The less the clock

cycles, the faster the DRAM

performance.

Row Precharge Time

(Trp)

Read only

This item controls the number of cycles

for Row Address Strobe (RAS) to be

allowed to precharge. If insufficient

time is allowed for the RAS to

accumulate its chage before DRAM

refresh, refresh may be incomplete and

DRAM may fail to retain data. This

item applies only when synchronous

DRAM is installed in the system.

RAS/RAS Delay (Trrd)

Read only

Auto uses hardware compensation

values. Other values add to or subtract

from hardware generated value.

Recommended setting is Auto.

Row Cycle (Trc) Read only

Bits 7-4. RAS#-active to RAS#-active

or auto refresh of the same bank.

Asynchronous Latency Read only

Bits 3-0. This filed should be loaded

with a 4-bit value equal to the

maximum asynchronous latency in the

DRAM read round-trip loop.

67