PCI-X v5.1 165 Getting Started Guide www.xilinx.com 35

UG158 March 24, 2008

Synplicity Synplify

10. Click Change Result File to display the EDIF Result File dialog box; then move the to

following directory:

<Install Path>/verilog/example/synthesis

11. Name the file pcix_top_s.edf and click OK to set the name of the result file and

return to the main project window.

Note:

In practice, the directory for the EDIF result file does not need to be changed. However,

the sample processing scripts included with the example design assume that the output EDIF

files will be located in the synthesis directory.

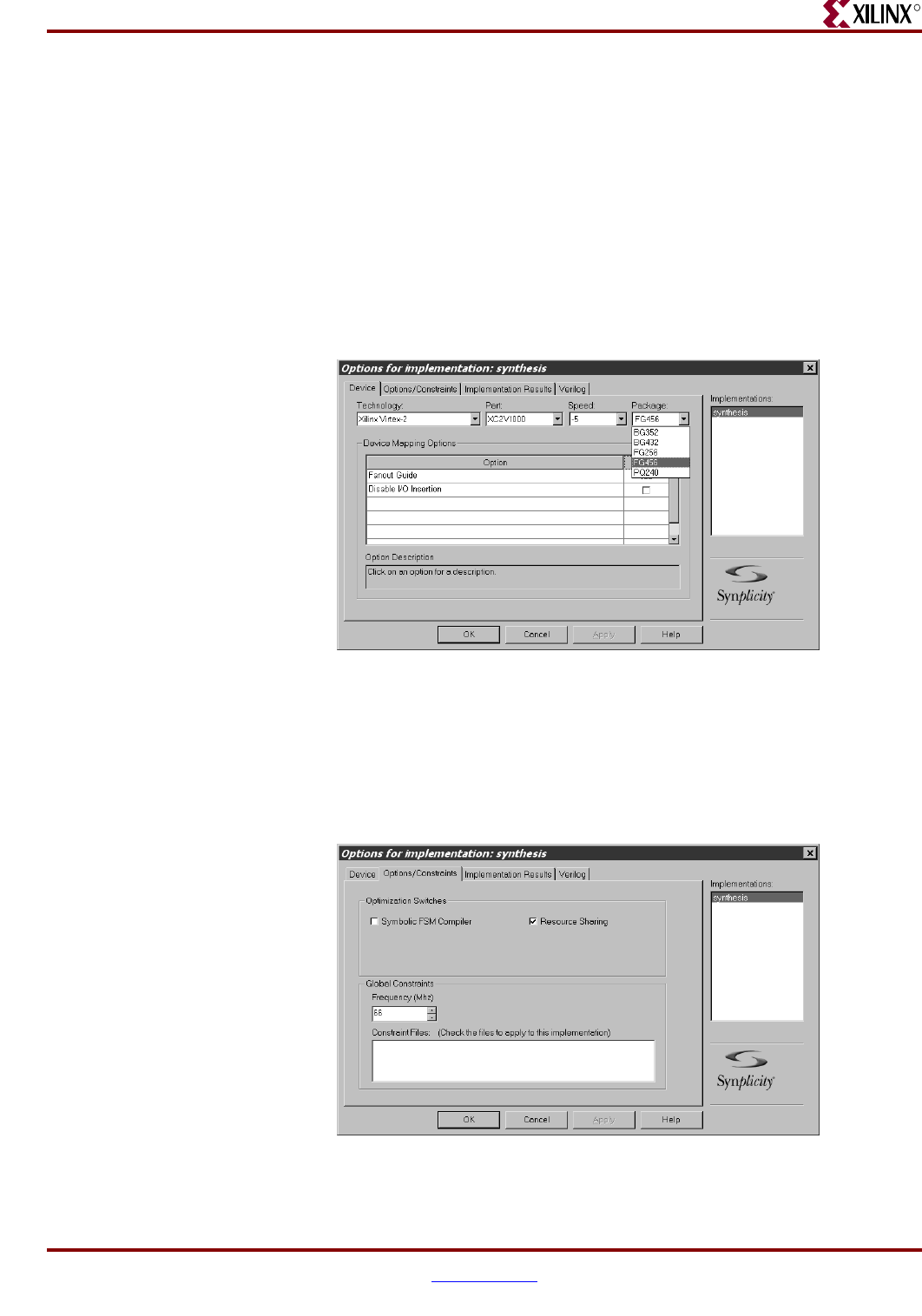

12. From the main project window, click Change Target to display the Options for

Implementation dialog, Figure 5-7.

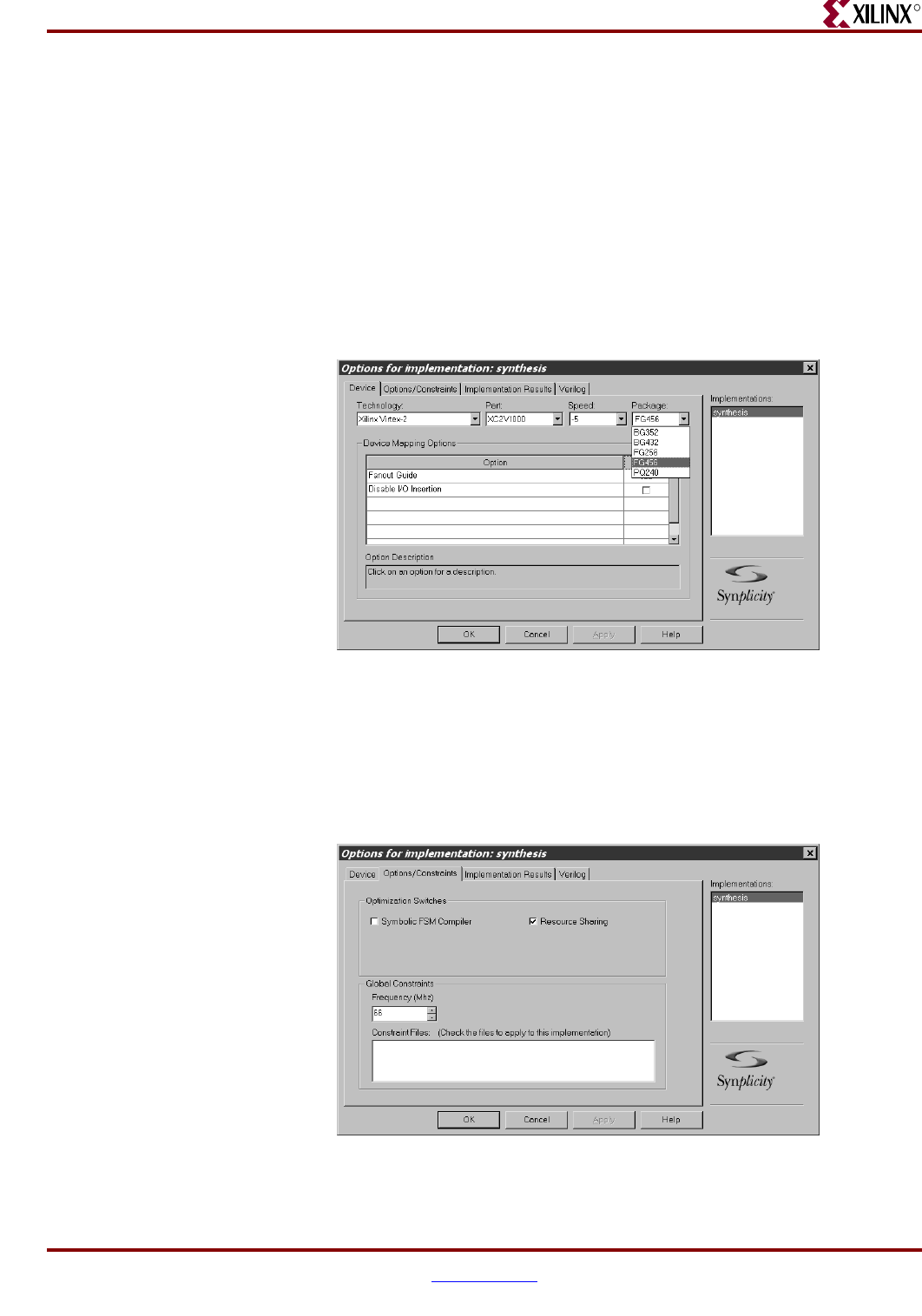

13. On the Device tab, set the Technology, Part, Speed, and Package options to reflect the

targeted device (a 2V1000FG456-5 in this example). Be sure that Disable I/O Insertion

is deselected.

14. On the Options/Constraints tab, deselect Symbolic FSM Compiler (but leave Resource

Sharing selected) and set the Frequency to 66 MHz.

Figure 5-7: Options for Implementation: Device

Figure 5-8: Options for Implementation: Options/Constraints