Rev. C | Page 44 of 48 | December 2006

ADSP-TS201S

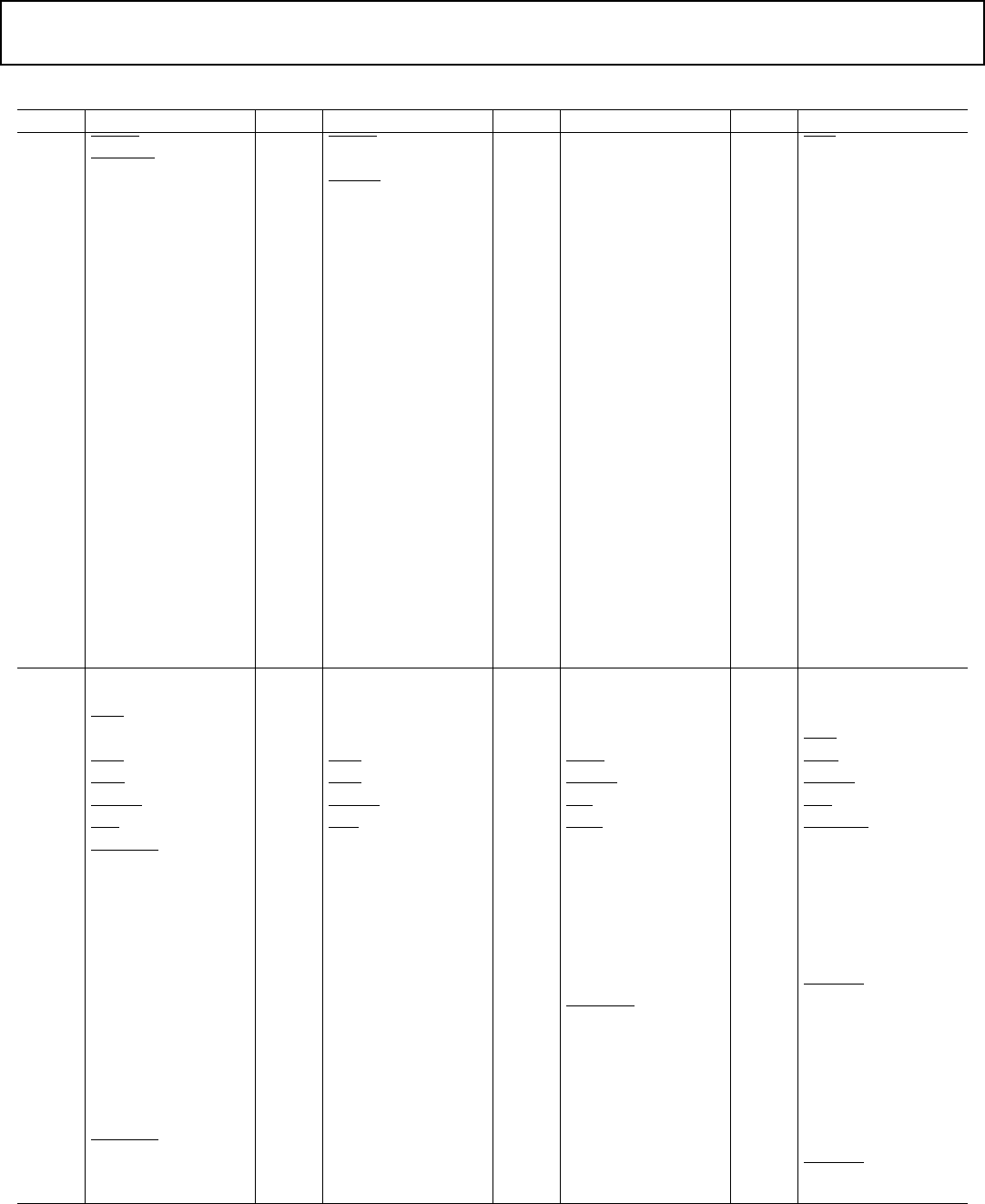

U1 MSSD0 V1 MSSD2 W1 CONTROLIMP0 Y1 EMU

U2 RST_OUT V2 DS2 W2 ENEDREG Y2 TCK

U3 ID2 V3 POR_IN W3 TDI Y3 TMR0E

U4 DS1 V4 CONTROLIMP1 W4 TDO Y4 FLAG3

U5 V

DD_IO

V5 V

SS

W5 V

DD_IO

Y5 V

SS

U6 V

DD

V6 V

DD

W6 V

DD

Y6 V

DD_IO

U7 V

DD

V7 V

DD

W7 V

DD

Y7 V

SS

U8 V

SS

V8 V

DD

W8 V

DD

Y8 V

DD_IO

U9 V

SS

V9 V

DD

W9 V

DD

Y9 V

SS

U10 V

DD

V10 V

DD

W10 V

DD

Y10 V

DD_IO

U11 V

DD_DRAM

V11 V

DD_DRAM

W11 V

DD_DRAM

Y11 V

DD_IO

U12 V

SS

V12 V

DD_DRAM

W12 V

DD_DRAM

Y12 V

DD_IO

U13 V

SS

V13 V

DD

W13 V

DD

Y13 V

DD_IO

U14 V

SS

V14 V

DD

W14 V

DD

Y14 V

DD_IO

U15 V

SS

V15 V

DD_DRAM

W15 V

DD_DRAM

Y15 V

DD_IO

U16 V

SS

V16 V

DD_DRAM

W16 V

DD_DRAM

Y16 V

SS

U17 V

SS

V17 V

DD

W17 V

DD

Y17 V

DD_IO

U18 V

DD

V18 V

DD

W18 V

DD

Y18 V

SS

U19 V

DD

V19 V

DD

W19 V

DD

Y19 V

DD_IO

U20 V

DD_IO

V20 V

DD_IO

W20 V

DD_IO

Y20 V

SS

U21 L1CLKINN V21 L1DATI3_N W21 L1CLKON Y21 L1DATO1_N

U22 L1CLKINP V22 L1DATI3_P W22 L1CLKOP Y22 L1DATO1_P

U23 L1DATI1_N V23 L1DATI2_N W23 L1DATO3_N Y23 L1DATO2_N

U24 L1DATI1_P V24 L1DATI2_P W24 L1DATO3_P Y24 L1DATO2_P

AA1 FLAG2 AB1 V

SS

AC1 FLAG0 AD1 V

SS

AA2 FLAG1 AB2 V

SS

AC2 V

SS

AD2 ID1

AA3 IRQ3 AB3 V

SS

AC3 V

DD_IO

AD3 V

DD_IO

AA4 V

SS

AB4 NC AC4 TMS AD4 TRST

AA5 IRQ0 AB5 IRQ2 AC5 IOWR AD5 IORD

AA6 IOEN AB6 IRQ1 AC6 DMAR2 AD6 DMAR3

AA7 DMAR0 AB7 DMAR1 AC7 CPA AD7 DPA

AA8 HBR AB8 HBG AC8 BOFF AD8 BUSLOCK

AA9 L3BCMPO AB9 L3ACKI AC9 L3DATO0_N AD9 L3DATO0_P

AA10 L3DATO1_N AB10 L3DATO1_P AC10 L3CLKON AD10 L3CLKOP

AA11 L3DATO3_N AB11 L3DATO3_P AC11 L3DATO2_N AD11 L3DATO2_P

AA12 V

SS

AB12 V

SS

AC12 L3DATI3_N AD12 L3DATI3_P

AA13 L3DATI2_N AB13 L3DATI2_P AC13 L3CLKINN AD13 L3CLKINP

AA14 L3DATI1_N AB14 L3DATI1_P AC14 L3DATI0_N AD14 L3DATI0_P

AA15 NC AB15 V

SS

AC15 L3ACKO AD15 L3BCMPI

AA16 L2DATO0_N AB16 L2DATO0_P AC16 L2BCMPO AD16 L2ACKI

AA17 L2CLKON AB17 L2CLKOP AC17 L2DATO1_N AD17 L2DATO1_P

AA18 L2DATO3_N AB18 L2DATO3_P AC18 L2DATO2_N AD18 L2DATO2_P

AA19 L2CLKINN AB19 L2CLKINP AC19 L2DATI3_N AD19 L2DATI3_P

AA20 L2DATI1_N AB20 L2DATI1_P AC20 L2DATI2_N AD20 L2DATI2_P

AA21 V

SS

AB21 L2ACKO AC21 L2DATI0_N AD21 L2DATI0_P

AA22 L1BCMPO

AB22 V

SS

AC22 V

DD_IO

AD22 V

DD_IO

AA23 L1DATO0_N AB23 V

DD_IO

AC23 V

SS

AD23 L2BCMPI

AA24 L1DATO0_P AB24 V

DD_IO

AC24 L1ACKI AD24 V

SS

1

On revision 1.x silicon, the R2 and R3 balls are NC. On revision 0.x silicon, the R2 ball is SCLK, and the R3 ball is SCLK_V

REF

. For more information on SCLK and SCLK_V

REF

on revision 0.x silicon, see the EE-179: ADSP-TS20x TigerSHARC System Design Guidelines on the Analog Devices website (www.analog.com).

Table 35. 576-Ball (25 mm × 25 mm) BGA_ED Ball Assignments (Continued)

Ball No. Signal Name Ball No. Signal Name Ball No. Signal Name Ball No. Signal Name