– 45 –

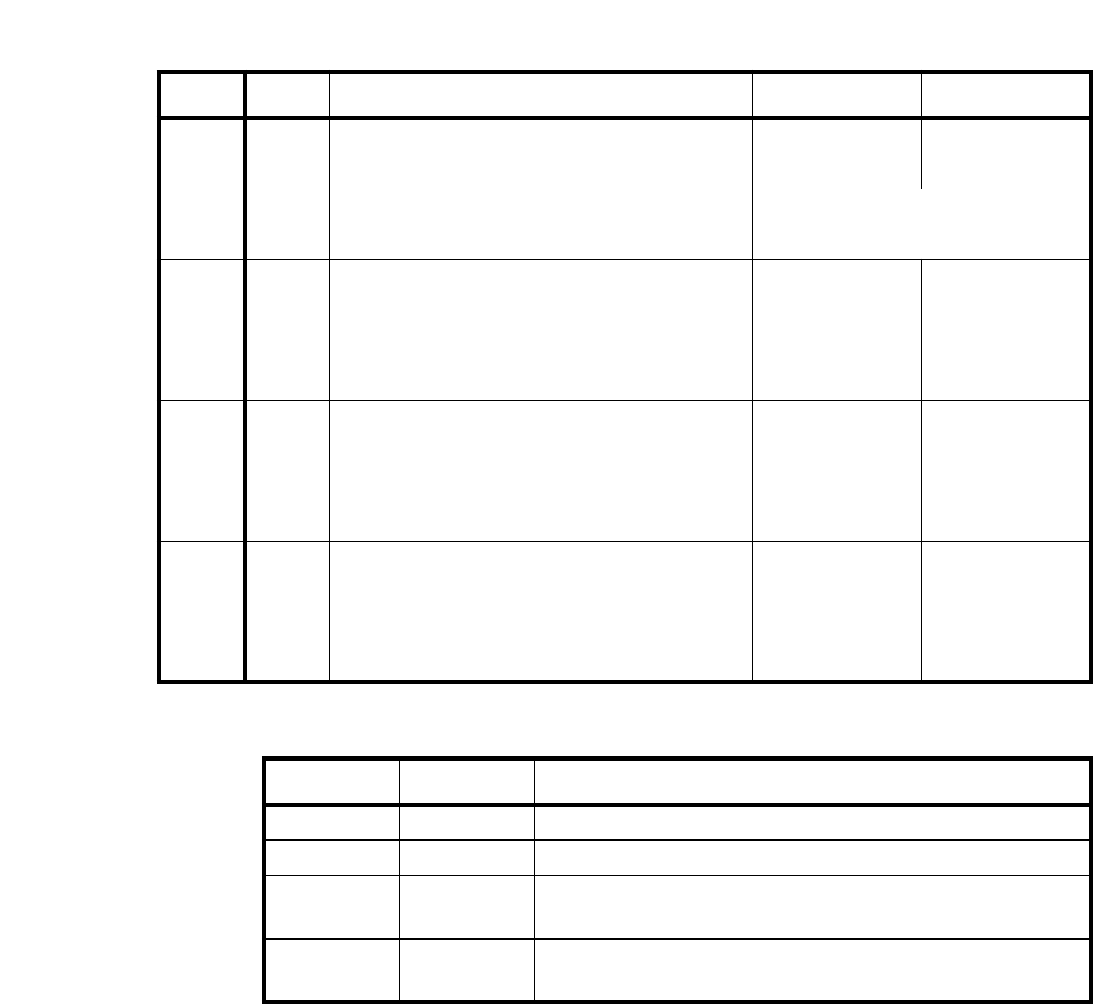

2) Memory Switch 5 (MSW5)

The setting upon shipment from the factory is indicated with “

*

”.

Bit Description

00

00

11

11

F

n1 E

D <ESC> "q" command function See Table below

(LSB) C <ESC> "q" command function See Table below

B

n2 A

9

(LSB) 8

7

n3 6

5

(LSB) 4

3

n4 2

1 Automatic clamp function Enabled

*

Disabled

(LSB) 0 Automatic head search function Enabled

*

Disabled

MSW5-D MSW5-C <ESC> “q” Command Function

0

*

0

*

Implements releasing

*

1 0 Implements releasing

0 1 Implements releasing after discharging all in the forward direction

(far side).

1 1 Implements releasing after discharging all in the reverse direction

(near side).