S1C6200/6200A CORE CPU MANUAL EPSON 17

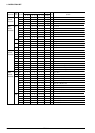

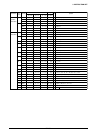

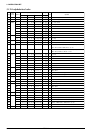

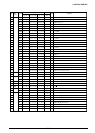

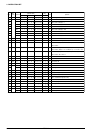

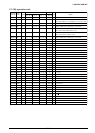

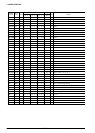

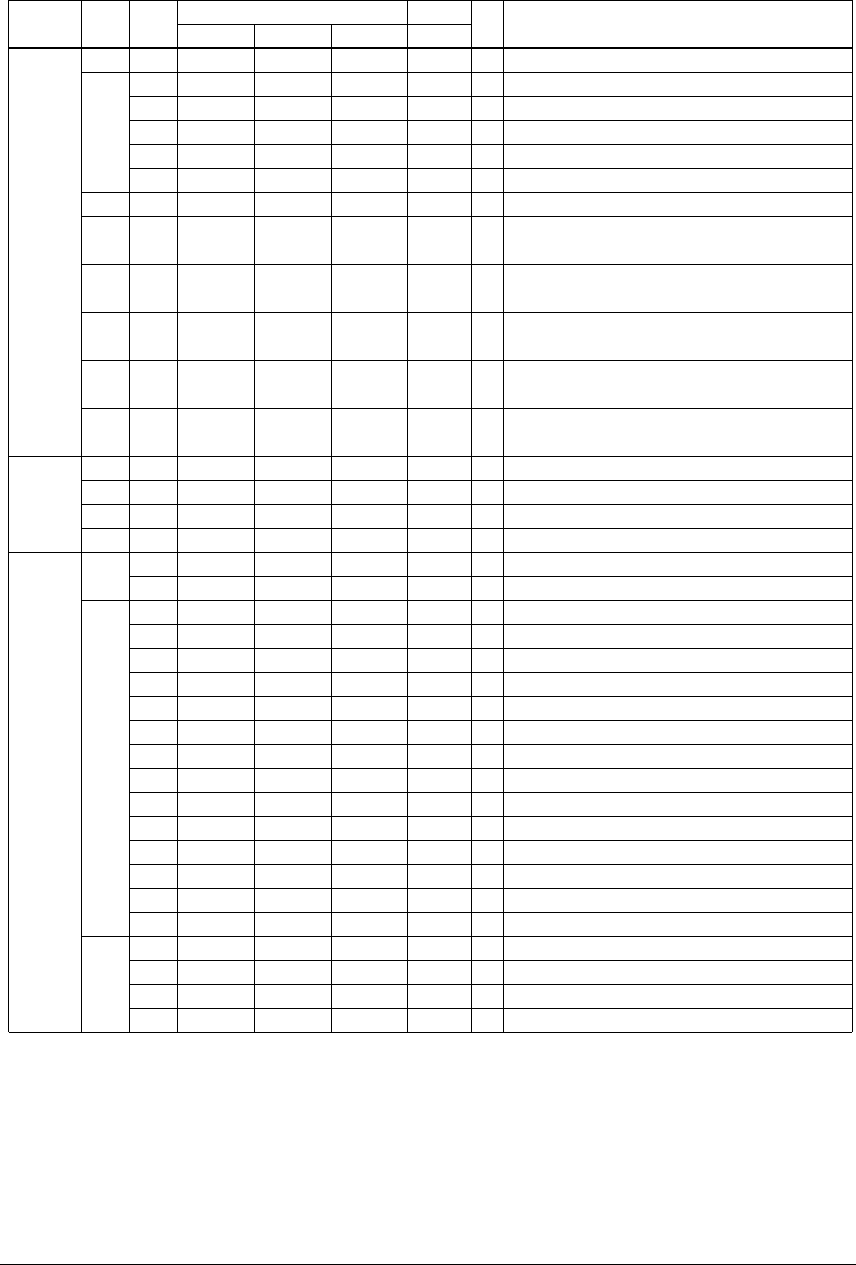

3 INSTRUCTION SET

3.1.1 By function

B

1

0

0

0

0

0

1

0

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

A

1

0

0

0

1

1

1

1

1

1

1

0

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

9

1

0

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

8

0

0

0

1

0

1

1

0

1

1

1

1

1

1

1

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

7

0

s7

s7

s7

s7

s7

1

s7

s7

1

1

e7

1

1

1

1

1

1

e7

e7

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

6

1

s6

s6

s6

s6

s6

1

s6

s6

1

1

e6

1

1

1

1

1

1

e6

e6

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

5

0

s5

s5

s5

s5

s5

1

s5

s5

0

0

e5

1

1

1

1

1

1

e5

e5

0

0

0

0

0

0

1

1

1

1

1

1

0

0

1

1

4

p4

s4

s4

s4

s4

s4

0

s4

s4

1

1

e4

1

1

1

1

0

1

e4

e4

0

0

0

1

1

1

0

0

0

1

1

1

0

1

0

1

3

p3

s3

s3

s3

s3

s3

1

s3

s3

1

1

e3

1

1

1

1

0

0

e3

e3

0

0

1

0

0

1

0

0

1

0

0

1

i3

i3

i3

i3

2

p2

s2

s2

s2

s2

s2

0

s2

s2

1

1

e2

0

1

0

0

0

0

e2

e2

0

1

0

0

1

0

0

1

0

0

1

0

i2

i2

i2

i2

1

p1

s1

s1

s1

s1

s1

0

s1

s1

1

1

e1

1

1

0

0

0

0

e1

e1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

i1

i1

i1

i1

0

p0

s0

s0

s0

s0

s0

0

s0

s0

1

0

e0

1

1

0

1

0

0

e0

e0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

i0

i0

i0

i0

p

s

C, s

NC, s

Z, s

NZ, s

s

s

e

X

Y

X, e

Y, e

XP, r

XH, r

XL, r

YP, r

YH, r

YL, r

r, XP

r, XH

r, XL

r, YP

r, YH

r, YL

XH, i

XL, i

YH, i

YL, i

PSET

JP

JPBA

CALL

CALZ

RET

RETS

RETD

NOP5

NOP7

HALT

SLP

INC

LD

ADC

IDZC

↑

↑

↑

↑

↑

↑

↑

↑

5

5

5

5

5

5

5

7

7

7

12

12

5

7

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

7

7

7

7

NBP

←

p4, NPP

←

p3~p0

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if C=1

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if C=0

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if Z=1

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if Z=0

PCB

←

NBP, PCP

←

NPP, PCSH

←

B, PCSL

←

A

M(SP-1)

←

PCP, M(SP-2)

←

PCSH, M(SP-3)

←

PCSL+1

SP

←

SP-3, PCP

←

NPP, PCS

←

s7~s0

M(SP-1)

←

PCP, M(SP-2)

←

PCSH, M(SP-3)

←

PCSL+1

SP

←

SP-3, PCP

←

0, PCS

←

s7~s0

PCSL

←

M(SP), PCSH

←

M(SP+1), PCP

←

M(SP+2)

SP

←

SP+3

PCSL

←

M(SP), PCSH

←

M(SP+1), PCP

←

M(SP+2)

SP

←

SP+3, PC

←

PC+1

PCSL

←

M(SP), PCSH

←

M(SP+1), PCP

←

M(SP+2)

SP

←

SP+3, M(X)

←

e3~e0, M(X+1)

←

e7~e4, X

←

X+2

No operation (5 clock cycles)

No operation (7 clock cycles)

Halt (stop clock)

SLEEP (stop oscillation)

X

←

X+1

Y

←

Y+1

XH

←

e7~e4, XL

←

e3~e0

YH

←

e7~e4, YL

←

e3~e0

XP

←

r

XH

←

r

XL

←

r

YP

←

r

YH

←

r

YL

←

r

r

←

XP

r

←

XH

r

←

XL

r

←

YP

r

←

Y

H

r

←

YL

XH

←

XH+i3~i0+C

XL

←

XL+i3~i0+C

YH

←

YH+i3~i0+C

YL

←

YL+i3~i0+C

↓

↓

↓

↓

↓

↓

↓

↓

Branch

instructions

System

control

instructions

Index

operation

instructions

Classification Operand Clock

Operation Code Flag

Mne-

monic

Operation