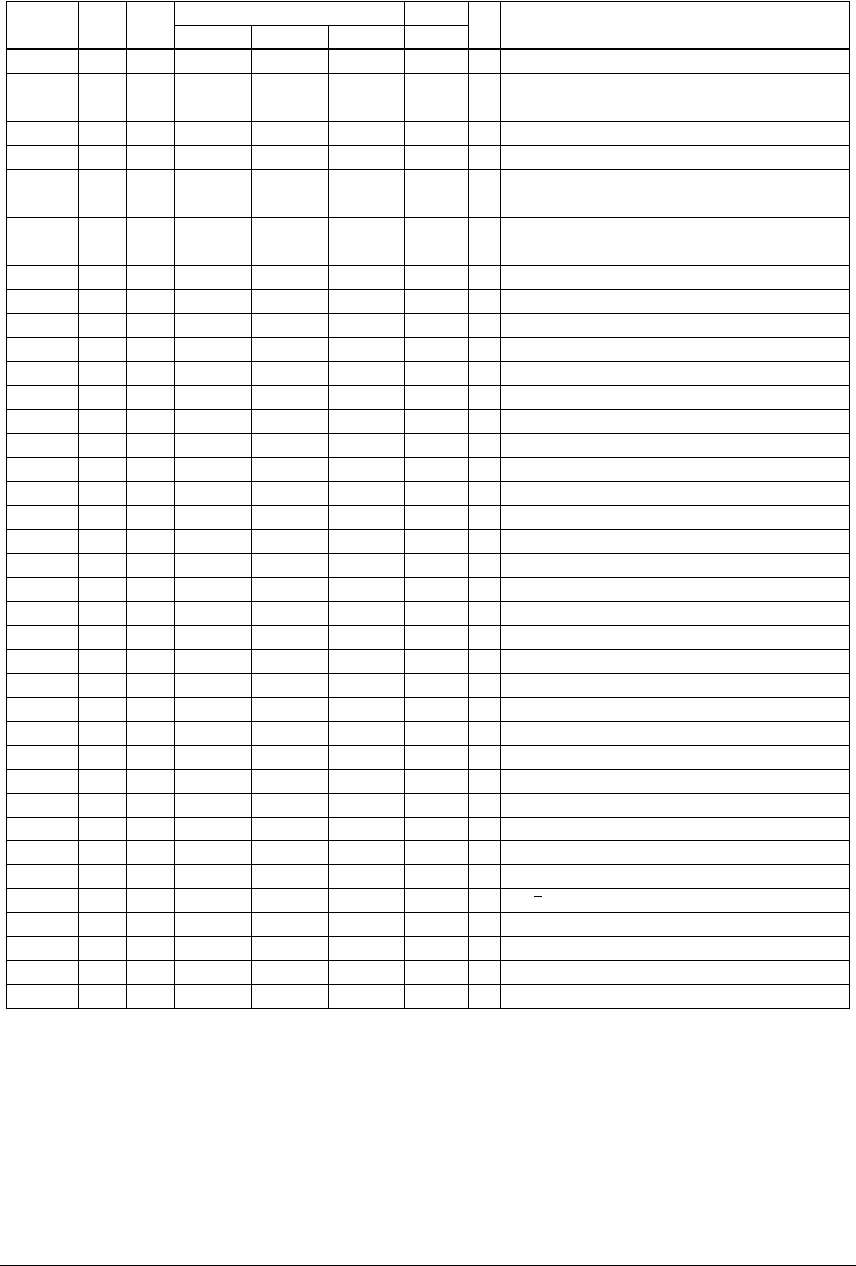

S1C6200/6200A CORE CPU MANUAL EPSON 23

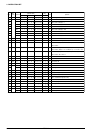

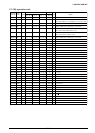

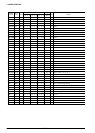

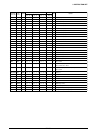

3 INSTRUCTION SET

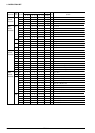

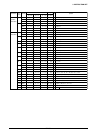

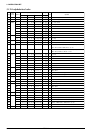

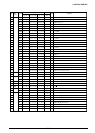

3.1.3 By operation code

B

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

A

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

9

0

0

1

1

0

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

1

8

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

1

1

1

1

0

7

s7

e7

s7

s7

s7

s7

s7

s7

e7

e7

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

e7

0

0

1

1

0

0

0

1

1

0

6

s6

e6

s6

s6

s6

s6

s6

s6

e6

e6

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

e6

0

1

0

1

0

0

1

0

1

0

5

s5

e5

s5

s5

s5

s5

s5

s5

e5

e5

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

e5

r1

r1

r1

r1

r1

r1

r1

r1

r1

r1

4

s4

e4

s4

s4

s4

s4

s4

s4

e4

e4

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

e4

r0

r0

r0

r0

r0

r0

r0

r0

r0

r0

3

s3

e3

s3

s3

s3

s3

s3

s3

e3

e3

i3

i3

i3

i3

i3

i3

i3

i3

r1

r1

r1

r1

r1

r1

r1

r1

e3

i3

i3

i3

i3

i3

1

i3

i3

i3

i3

2

s2

e2

s2

s2

s2

s2

s2

s2

e2

e2

i2

i2

i2

i2

i2

i2

i2

i2

r0

r0

r0

r0

r0

r0

r0

r0

e2

i2

i2

i2

i2

i2

1

i2

i2

i2

i2

1

s1

e1

s1

s1

s1

s1

s1

s1

e1

e1

i1

i1

i1

i1

i1

i1

i1

i1

q1

q1

q1

q1

q1

q1

q1

r1

e1

i1

i1

i1

i1

i1

1

i1

i1

i1

i1

0

s0

e0

s0

s0

s0

s0

s0

s0

e0

e0

i0

i0

i0

i0

i0

i0

i0

i0

q0

q0

q0

q0

q0

q0

q0

r0

e0

i0

i0

i0

i0

i0

1

i0

i0

i0

i0

s

e

C, s

NC, s

s

s

Z, s

NZ, s

Y, e

MX, e

XH, i

XL, i

YH, i

YL, i

XH, i

XL, i

YH, i

YL, i

r, q

r, q

r, q

r, q

r, q

r, q

r, q

r

X, e

r, i

r, i

r, i

r, i

r, i

r

r, i

r, i

r, i

r, i

JP

RETD

JP

JP

CALL

CALZ

JP

JP

LD

LBPX

ADC

ADC

ADC

ADC

CP

CP

CP

CP

ADD

ADC

SUB

SBC

AND

OR

XOR

RLC

LD

ADD

ADC

AND

OR

XOR

NOT

SBC

FAN

CP

LD

IDZC

★

★

★

★

★

★

★

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

5

12

5

5

7

7

5

5

5

5

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

5

7

7

7

7

7

7

7

7

7

5

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0

PCSL

←

M(SP), PCSH

←

M(SP+1), PCP

←

M(SP+2)

SP

←

SP+3, M(X)

←

e3~e0, M(X+1)

←

e7~e4, X

←

X+2

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if C=1

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if C=0

M(SP-1)

←

PCP, M(SP-2)

←

PCSH, M(SP-3)

←

PCSL+1

SP

←

SP-3, PCP

←

NPP, PCS

←

s7~s0

M(SP-1)

←

PCP, M(SP-2)

←

PCSH, M(SP-3)

←

PCSL+1

SP

←

SP-3, PCP

←

0, PCS

←

s7~s0

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if Z=1

PCB

←

NBP, PCP

←

NPP, PCS

←

s7~s0 if Z=0

YH

←

e7~e4, YL

←

e3~e0

M(X)

←

e3~e0, M(X+1)

←

e7~e4, X

←

X+2

XH

←

XH+i3~i0+C

XL

←

XL+i3~i0+C

YH

←

YH+i3~i0+C

YL

←

YL+i3~i0+C

XH-i3~i0

XL-i3~i0

YH-i3~i0

YL-i3~i0

r

←

r+q

r

←

r+q+C

r

←

r-q

r

←

r-q-C

r

←

rΛq

r

←

rVq

r

←

r∀q

d3

←

d2, d2

←

d1, d1

←

d0, d0

←

C, C

←

d3

XH

←

e7~e4, XL

←

e3~e0

r

←

r+i3~i0

r

←

r+i3~i0+C

r

←

rΛi3~i0

r

←

rVi3~i0

r

←

r∀i3~i0

r

←

r

r

←

r-i3~i0-C

rΛi3~i0

r-i3~i0

r

←

i3~i0

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

000 to 0FF

100 to 1FF

200 to 2FF

300 to 3FF

400 to 4FF

500 to 5FF

600 to 6FF

700 to 7FF

800 to 8FF

900 to 9FF

A00 to A0F

A10 to A1F

A20 to A2F

A30 to A3F

A40 to A4F

A50 to A5F

A60 to A6F

A70 to A7F

A80 to A8F

A90 to A9F

AA0 to AAF

AB0 to ABF

AC0 to ACF

AD0 to ADF

AE0 to AEF

AF0 to AFF

B00 to BFF

C00 to C3F

C40 to C7F

C80 to CBF

CC0 to CFF

D00 to D3F

D0F to D3F

D40 to D7F

D80 to DBF

DC0 to DFF

E00 to E3F

Operand Clock

Operation Code Flag

Mne-

monic

Operation

Operation

Code (HEX)