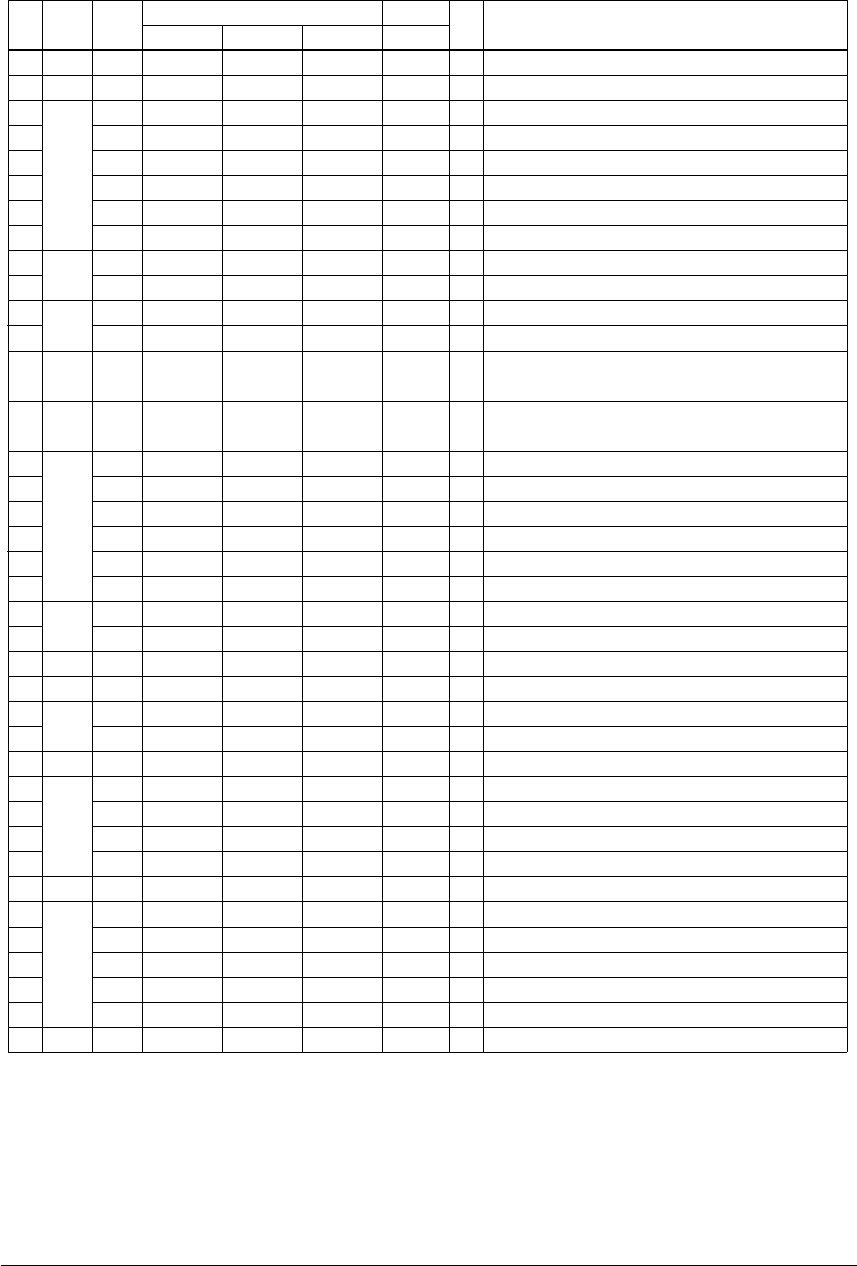

20 EPSON S1C6200/6200A CORE CPU MANUAL

3 INSTRUCTION SET

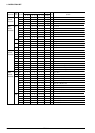

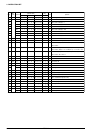

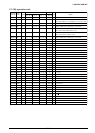

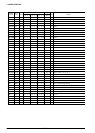

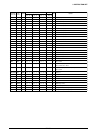

3.1.2 In alphabetical order

B

1

1

1

1

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

A

1

1

1

0

0

0

0

0

1

0

1

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

1

0

1

0

9

1

1

0

1

1

1

1

1

0

1

0

1

0

0

0

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

0

1

0

8

1

1

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

1

0

1

1

0

0

1

7

0

0

0

1

0

0

0

0

0

1

1

1

s7

s7

1

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

1

1

s7

s7

s7

s7

s7

e7

6

0

0

1

0

0

0

0

0

0

0

0

1

s6

s6

1

0

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

s6

s6

s6

s6

s6

e6

5

1

1

r1

0

0

0

1

1

r1

0

r1

0

s5

s5

r1

0

0

0

1

1

1

0

0

0

r1

0

1

1

0

1

1

1

s5

s5

s5

s5

s5

e5

4

0

0

r0

1

0

1

0

1

r0

0

r0

0

s4

s4

r0

0

0

1

0

1

1

0

1

0

r0

1

1

0

1

0

1

0

s4

s4

s4

s4

s4

e4

3

1

1

i3

r1

i3

i3

i3

i3

i3

r1

i3

r1

s3

s3

i3

r1

i3

i3

i3

i3

n3

1

0

1

i3

r1

1

n3

1

0

0

1

s3

s3

s3

s3

s3

e3

2

0

1

i2

r0

i2

i2

i2

i2

i2

r0

i2

r0

s2

s2

i2

r0

i2

i2

i2

i2

n2

0

1

0

i2

r0

0

n2

0

0

0

0

s2

s2

s2

s2

s2

e2

1

r1

r1

i1

q1

i1

i1

i1

i1

i1

q1

i1

q1

s1

s1

i1

q1

i1

i1

i1

i1

n1

1

1

0

i1

q1

0

n1

1

0

0

0

s1

s1

s1

s1

s1

e1

0

r0

r0

i0

q0

i0

i0

i0

i0

i0

q0

i0

q0

s0

s0

i0

q0

i0

i0

i0

i0

n0

1

1

0

i0

q0

0

n0

1

0

0

0

s0

s0

s0

s0

s0

e0

MX, r

MY, r

r, i

r, q

XH, i

XL, i

YH, i

YL, i

r, i

r, q

r, i

r, q

s

s

r, i

r, q

XH, i

XL, i

YH, i

YL, i

Mn

SP

r, i

r, q

Mn

SP

X

Y

C, s

NC, s

NZ, s

s

Z, s

MX, e

ACPX

ACPY

ADC

ADD

AND

CALL

CALZ

CP

DEC

DI

EI

FAN

HALT

INC

JPBA

JP

LBPX

IDZC

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

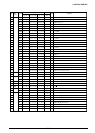

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

5

7

7

7

7

5

7

5

5

5

5

5

5

5

5

5

5

M(X)

← M(X)+r+C, X ← X+1

M(Y)

← M(Y)+r+C, Y ← Y+1

r

← r+i3~i0+C

r

← r+q+C

XH

← XH+i3~i0+C

XL

← XL+i3~i0+C

YH

← YH+i3~i0+C

YL

← YL+i3~i0+C

r

← r+i3~i0

r

← r+q

r

← rΛi3~i0

r

← rΛq

M(SP-1)

← PCP, M(SP-2) ← PCSH, M(SP-3) ← PCSL+1

SP

← SP-3, PCP ← NPP, PCS ← s7~s0

M(SP-1)

← PCP, M(SP-2) ← PCSH, M(SP-3) ← PCSL+1

SP

← SP-3, PCP ← 0, PCS ← s7~s0

r-i3~i0

r-q

XH-i3~i0

XL-i3~i0

YH-i3~i0

YL-i3~i0

M(n3~n0)

← M(n3~n0)-1

SP

← SP-1

I

← 0 (Disables Interrupt)

I

← 1 (Enables Interrupt)

rΛi3~i0

rΛq

Halt (stop clock)

M(n3~n0)

← M(n3~n0)+1

SP

← SP+1

X

← X+1

Y

← Y+1

PCB

← NBP, PCP ← NPP, PCSH ← B, PCSL ← A

PCB

← NBP, PCP ← NPP, PCS ← s7~s0 if C=1

PCB

← NBP, PCP ← NPP, PCS ← s7~s0 if C=0

PCB

← NBP, PCP ← NPP, PCS ← s7~s0 if Z=0

PCB

← NBP, PCP ← NPP, PCS ← s7~s0

PCB

← NBP, PCP ← NPP, PCS ← s7~s0 if Z=1

M(X)

← e3~e0, M(X+1) ← e7~e4, X ← X+2

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

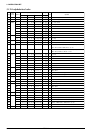

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

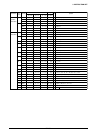

Page Operand Clock

Operation Code Flag

Mne-

monic

Operation

↓

↑

★

★

★

★

★

★

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓