21

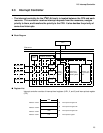

2.2 Lock Control Block

■

Description of Operation

Main/sub clock block has normal and low-power consumption mode. The low-power

consumption mode are described below.

(1) Low-power consumption mode

This chip has three operation modes. The sleep mode and stop mode in the table below reduce

the power consumption.

• The SLEEP mode stops only the operating clock pulse of the CPU. Other operations are

continued.

• The STOP mode stops the oscillation. Data can be held with the lowest power consumption

in this mode.

(a) SLEEP state

• Switching to Sleep State

• Writing 1 at the SLP bit (bit6) of the STBC register switches the mode to SLEEP state.

• The SLEEP state is the mode to stop clock pulse operating the CPU. Only the CPU

stops and the resources continue to operate.

• If an interrupt is requested when 1 is written at the SLP bit (bit 6), instruction execution

continues without switching to the SLEEP state.

• In the SLEEP state, the values of registers and RAM immediately before entering the

SLEEP state are held.

• Cancelling SLEEP state

• The SLEEP state is cancelled by inputting the reset signal and requesting an interrupt.

• When the reset signal is input during the SLEEP state, the CPU is switched to the reset

state and the SLEEP state is cancelled.

• When an interrupt level higher than 11 is requested from a resource during the SLEEP

state, the SLEEP state is cancelled.

• When the I flag and IL bit are enabled interrupt like an ordinary interrupt after cancelling,

the CPU executes the interrupt processing. When they are disabled, the CPU executes

the interrupt processing from the instruction next to the one before entering the SLEEP

state.

(b) STOP state

• Switching to STOP state

• Writing 1 at the STP bit (bit7) of the STBC register switches the mode to STOP state.

• In the STOP state, the clock oscillation, CPU, and all resources are stopped.

Table 2.2-1 Opeating State of Low-power Consumption Modes

Clock mode

of CPU

Clock pulse

Each operating clock pulse

(4 Mhz clock)

Wake-up source

in each mode

CPU

Time base

timer

Each

resource

RUN

Oscillates

2.0 MHz

2.0 MHz 2.0 MHz

Various interrupt

requests

Sleep

Stops