5 - 40 C141-E116-01EN

• Both devices shall execute self-diagnosis.

• The device 0 waits for up to 5 seconds until device 1 asserts the PDIAG- signal.

• If the device 1 does not assert the PDIAG- signal but indicates an error, the device 0 shall

append X‘80’ to its own diagnostic status.

• The device 0 clears the BSY bit of the Status register and generates an interrupt. (The device

1 does not generate an interrupt.)

• A diagnostic status of the device 0 is read by the host system. When a diagnostic failure of the

device 1 is detected, the host system can read a status of the device 1 by setting the DV bit

(selecting the device 1).

When device 1 is not present:

• The device 0 posts only the results of its own self-diagnosis.

• The device 0 clears the BSY bit of the Status register, and generates an interrupt.

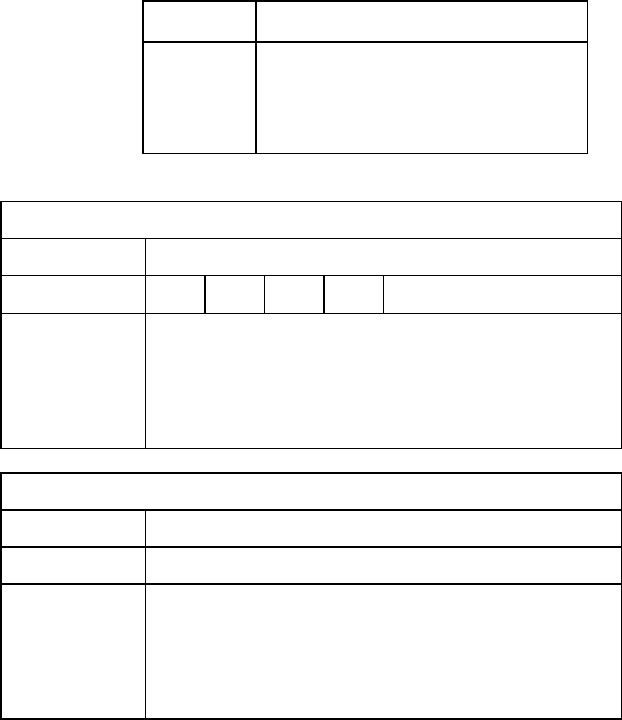

Table 5.7 lists the diagnostic code written in the Error register which is 8-bit code.

If the device 1 fails the self-diagnosis, the device 0 "ORs" X‘80’ with its own status and sets that

code to the Error register.

Table 5.7 Diagnostic code

Code Result of diagnostic

X‘01’

X‘03’

X‘05’

X‘8x’

No error detected.

Data buffer compare error

ROM sum check error

Failure of device 1

At command issuance (I/O registers setting contents)

1F7

H

(CM) 10010000

1F6

H

(DH)

×××

DV xx

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(FR)

xx

xx

xx

xx

xx

At command completion (I/O registers contents to be read)

1F7

H

(ST) Status information

1F6

H

(DH) 00

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

00

00

01

H

01

H

Diagnostic code