EM78P221/2N

8-Bit Microcontroller with OTP ROM

8 •

Product Specification (V1.0) 10.19.2007

(This specification is subject to change without further notice)

6.2 Registers Description

6.2.1 A (Accumulator)

Internal data transfer operation, or instruction operand holding usually involves the

temporary storage function of the Accumulator. The Accumulator is not an

addressable register.

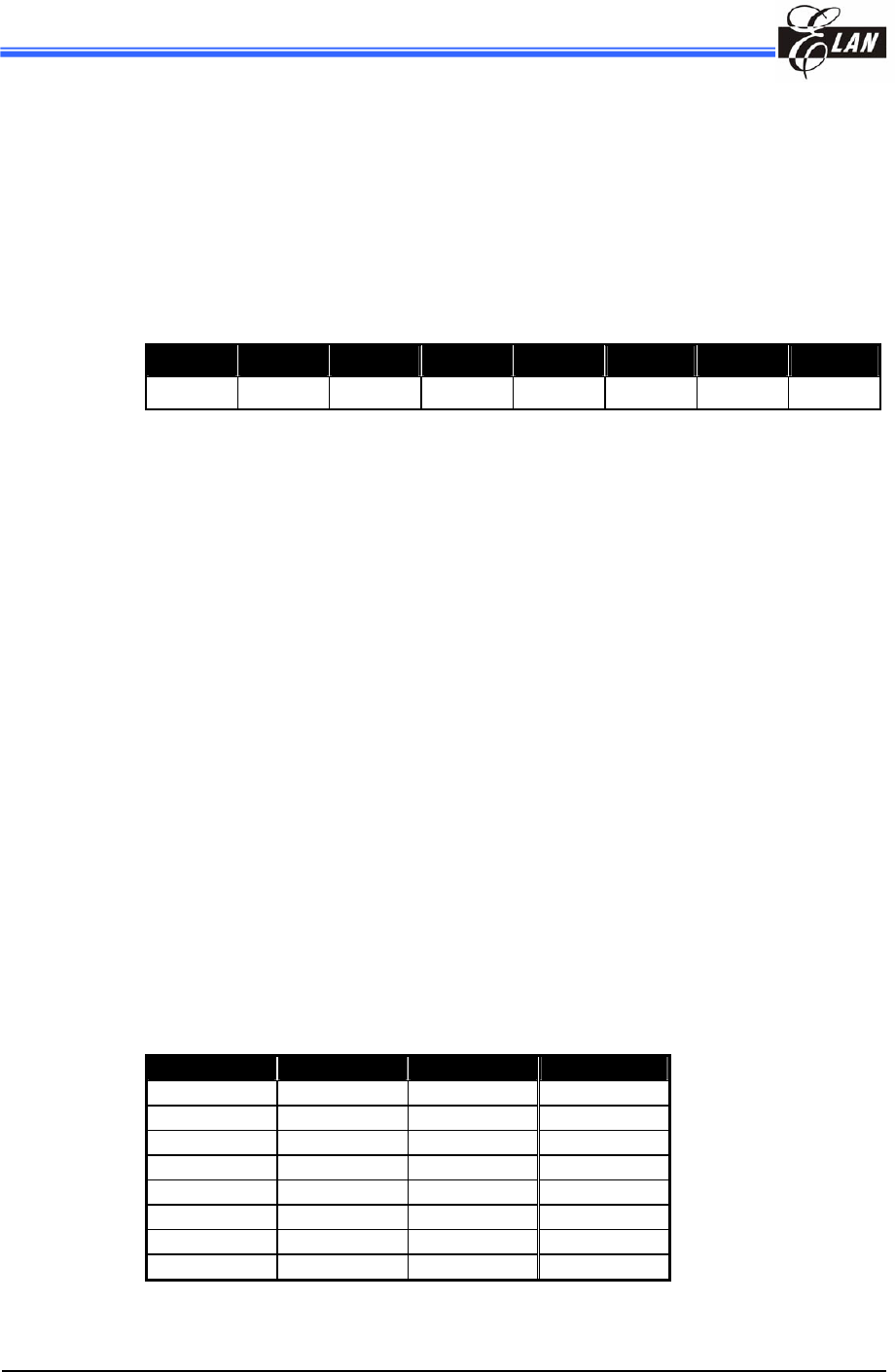

6.2.2 CONT (Control Register)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

INTE INT TS TE PSTE PST2 PST1 PST0

Bit 7 (INTE): INT signal edge

0 = interrupt occurs at the rising edge on the INT0 and INT1 pin

1 = interrupt occurs at the falling edge on the INT0 and INT1 pin

Bit 6 (INT): Interrupt enable flag

0 = masked by DISI or hardware interrupt

1 = enabled by the ENI/RETI instructions

This bit is readable only.

Bit 5 (TS): TCC signal source

0 = internal instruction cycle clock. If P56 is used as I/O pin, TS must be 0.

1 = transition on the TCC pin

Bit 4 (TE): TCC signal edge

0 = increment if the transition from low to high takes place on the TCC pin

1 = increment if the transition from high to low takes place on the TCC pin.

Bit 3 (PSTE): Prescaler enable bit for TCC

0 = prescaler disable bit. TCC rate is 1:1

1 = prescaler enable bit. TCC rate is set as Bit 2 ~ Bit 0.

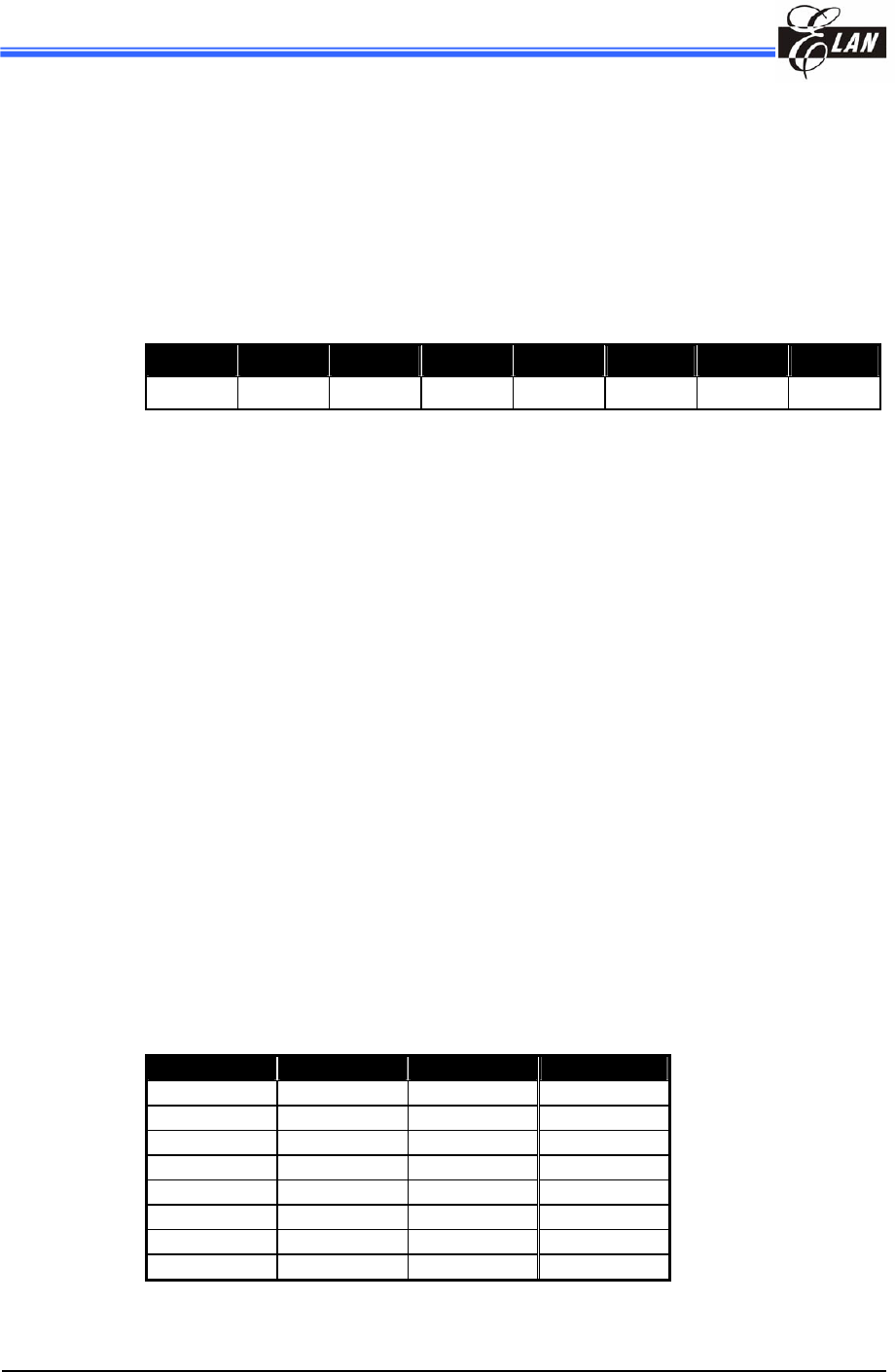

Bit 2 ~ Bit 0 (PST2 ~ PST0): TCC prescaler bits

PST2 PST1 PST0 TCC Rate

0 0 0 1:2

0 0 1 1:4

0 1 0 1:8

0 1 1 1:16

1 0 0 1:32

1 0 1 1:64

1 1 0 1:128

1 1 1 1:256

Note: Tcc time-out period [1/Fosc x prescaler x (256 -Tcc cnt) x 1]

Fosc: Oscillator (Crystal, ERC, IRC) frequency