EM78P221/2N

8-Bit Microcontroller with OTP ROM

Product Specification (V1.0) 10.19.2007 • 21

(This specification is subject to change without further notice)

6.2.31 Bank 3-R7 (Noise and LVR Control) - only for ICE

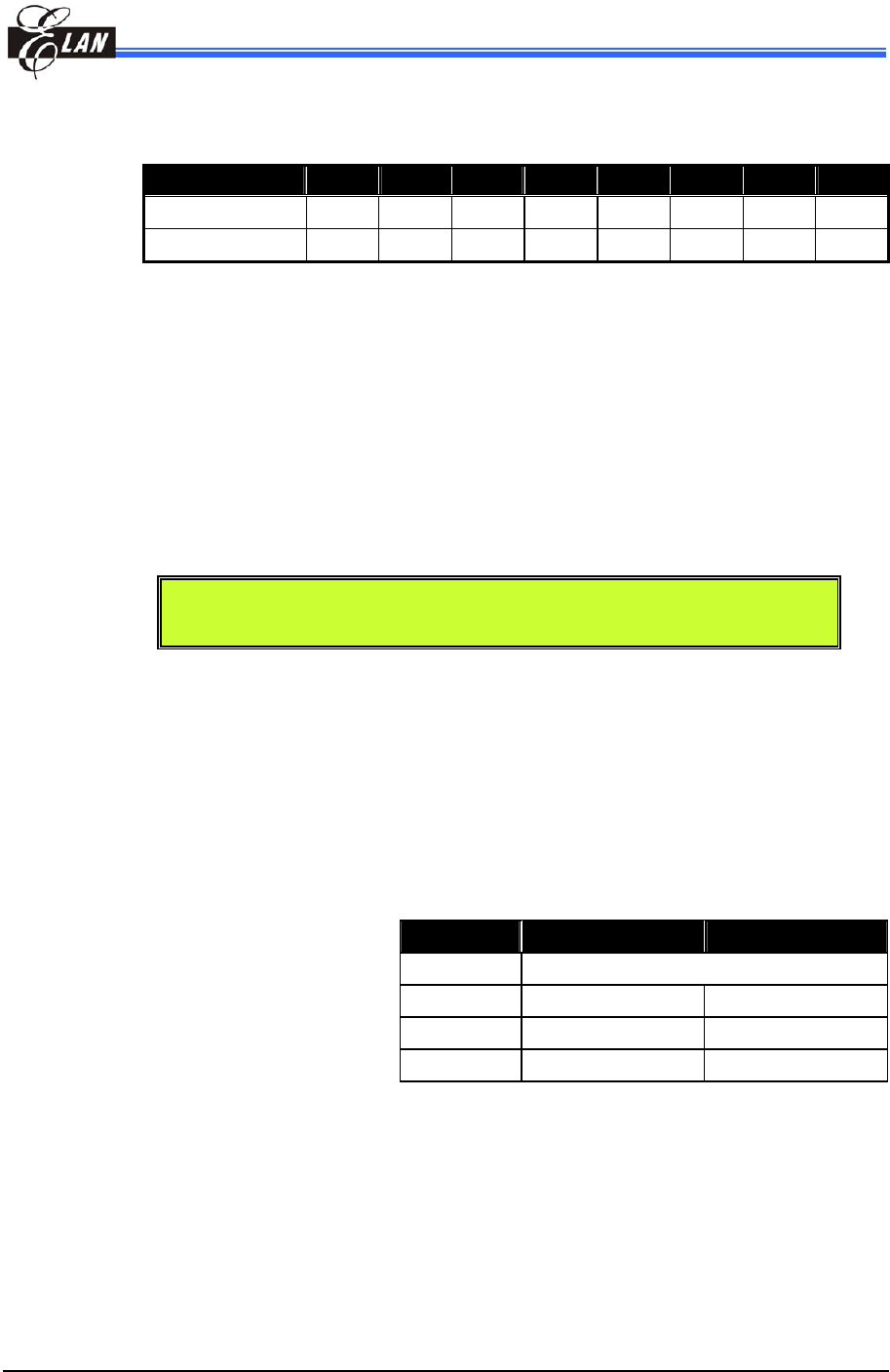

Bit 7 6 5 4 3 2 1 0

EM78P221/2N ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’

ICE220N “0” “0” “0” “0” NRHL NRE LVR1 LVR0

Bits 7 ~ 4: not used, fixed to "0" all the time.

Bits 3 ~ 0:

[With EM78P221/2N]: Unimplemented, read as ‘0’.

[With Simulator]:

Bit 3 (NRHL): Noise rejection high/low pulses define bit. The INT pin is a falling

edge trigger

0 = Pulses equal to 8/fc [s] are regarded as signal.

1 = Pulses equal to 32/fc [s] are regarded as signal (default)

NOTE

The noise rejection function is turned off in the LXT2 and sleep mode.

Bit 2 (NRE): Noise rejection enable

0 = disable noise rejection

1 = enable noise rejection (default). However in Low Crystal

oscillator (LXT) mode, the noise rejection circuit is always

disabled.

Bits 1 ~ 0 (LVR1 ~ LVR0): Low Voltage Reset enable bits. If Vdd has crossover at

Vdd reset level as Vdd changes, the system will be reset.

LVR1, LVR0 VDD Reset Level VDD Release Level

11 NA (Power-on Reset) (default)

10 2.5V 2.7V

01 3.0V 3.2V

00 4.0V 4.2V

6.2.32 Bank 3-R8~RF (Reserve)

Bits 7~0: not used, fixed to "0" all the time.

6.2.33 R10 ~ R1F

All of these are 8-bit general-purpose registers.

6.2.34 Banks 0~3 - R20 ~ R3F

All of these are 8-bit general-purpose registers.