NR - 6600

(9)

30

600-3100

9

1

(3)

1.9MB/NA1900768071409405-520

NR - 6600

(9)

30

600-3100

9

1

(3)

1.9MB/NA1900768171419405-520

NR - 6600

(9)

30

600-3100

9

1

(3)

1.9MB/NA1900768271429405-520

NR

-

6600

(9)

30

600

-

3100

9

1

(3)

1.9/NA1900735371569405-520

2600 - 8200

(9)

60

1200-3800

9

1

(3)

1.9/36MB1900768771489405-520

2600 - 8200

(9)

60

1200-3800

9

1

(3)

1.9/36MB1900735471439405-520

8200603800

1

1.9/36MB1900NA71449405-520

8200603800 1 1.9/36MB1900NA71529405-520

Express

NR - 660030

600-3100

9

1

(3)

1.9MB/NA1900735573509406-520

2600 - 820060

1200-3800

9

1

(3)

1.9/36MB190073577352 9406-520

Value

260012001200

1

(3)

1.9/36MB1900NA77349406-520

260012001200

1

(3)

1.9/36MB1900NA7373

(5)

9406-520

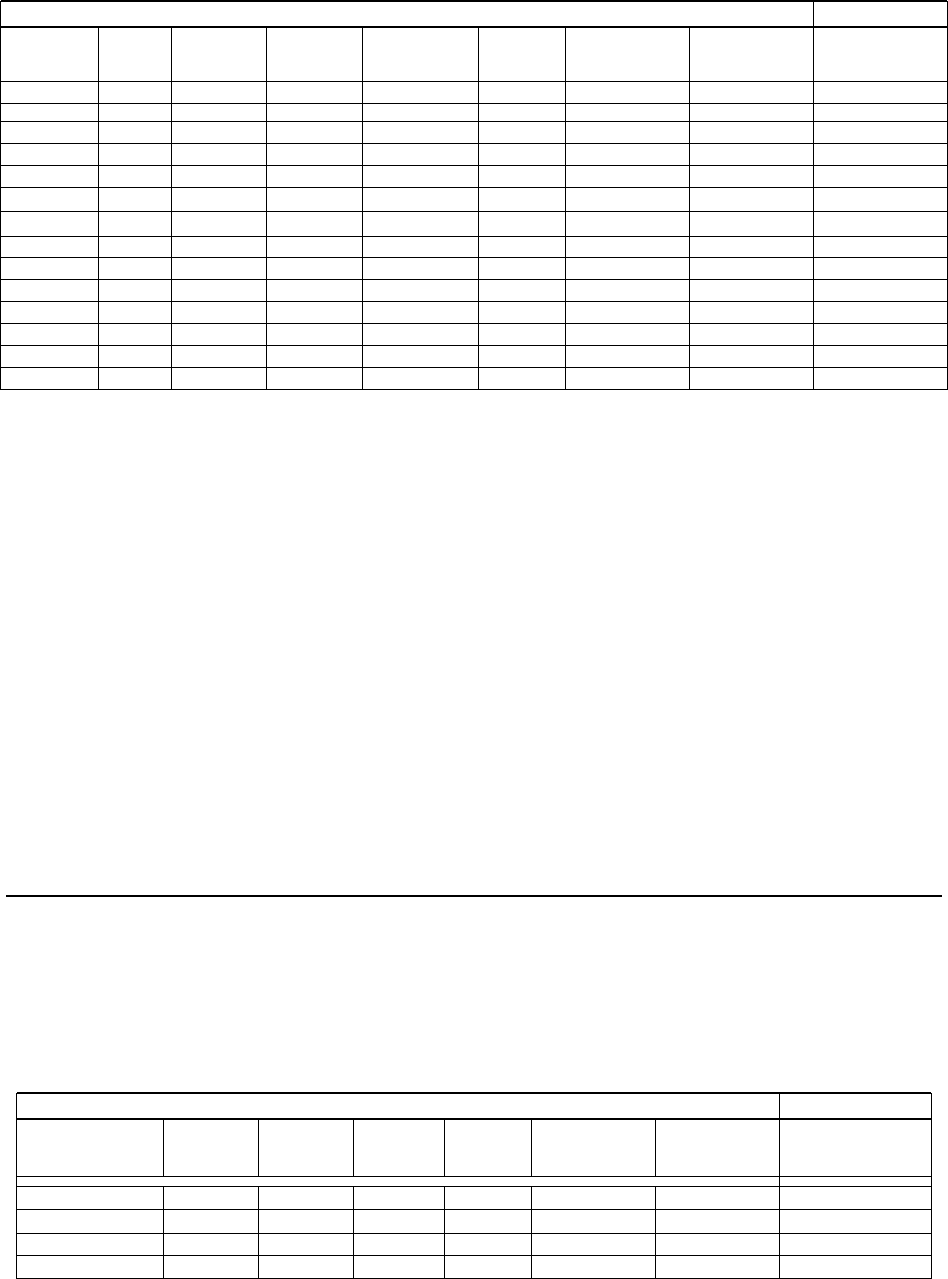

MCU

5250 OLTP

CPW

Processor

CPW

CPU

Range

L2/L3 cache

per CPU

(1)

Chip Speed

MHz

Accelerator

Feature

Edition

Feature

2

Model

Table C.6.1.1. System i models

*Note: 1. These models share L2 and L3 cache between two processor cores.

2. This is the Edition Feature for the model. This is the feature displayed when you display the

system value QPRCFEAT.

3. CPU Range -

entry model is a partial processor model, offering multiple price/performance

points for the entry market.

4. Capacity Backup model.

5. High Availability model.

6. Domino edition.

7. The MCU rating is a projected value.

8. The 64-way CPW value is reflects two 32-way partitions.

9. These models are accelerator models. The base CPW or MCU value is the capacity with the

default processor feature. The max CPW or MCU value is the capacity when

purchasing the accelerator processor feature.

10. Collaboration Edition. (Announced May 9, 2006)

11. User based pricing models.

12. These values listed are unconstrained CPW or MCU values (there is sufficient I/O such that

the processor would be the first constrained resource). The I/O constrained CPW value

for an 8-disk configuration is approximately 800 CPW (100 CPW per disk).

NR - Not Recommended: the 600 CPW processor offering is not recommended for Domino.

C.7 V5R3 Additions (May, July, August, October 2004, July 2005)

New for this release is the eServer i5 servers which provide a significant performance improvement when

compared to iSeries model 8xx servers.

C.7.1

IBM ~® i5 Servers

105000 -194000

(7)

046000-8500016 - 3236 MB1.9 MB1650595-0947 (7498)

105000 -194000

(7)

12000-85000

46000-8500016 - 3236 MB1.9 MB1650595-0947 (7499)

196000

(7)

-375000

(7)

086000-165000

32 - 64

(8

)

36 MB1.9 MB1650595-0952 (7484)

196000

(7)

-375000

(7)

12000-165000

86000-165000

32 - 64

(8

)

36 MB1.9 MB1650595-0952 (7485)

MCU

5250 OLTP

CPW

Processor

CPW

CPU

Range

L3 cache

per CPU

(

2)

L2 cache

per CPU

(1)

Chip Speed

MHz

Model

Table C.7.1.1. ~® i5 Servers

IBM i 6.1 Performance Capabilities Reference - January/April/October 2008

© Copyright IBM Corp. 2008 Appendix C CPW, CIW and MCU for System i Platform 350