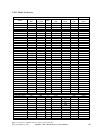

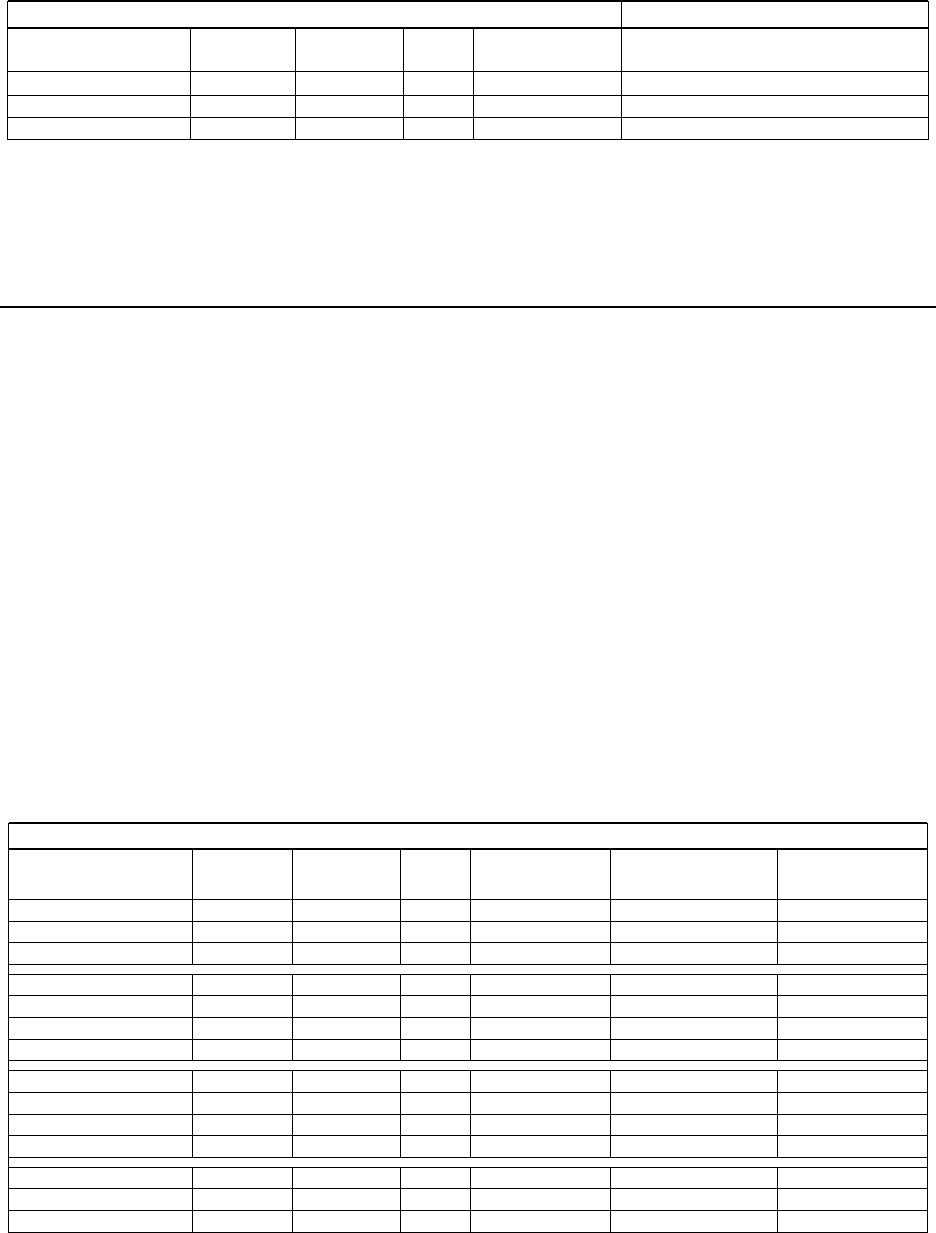

C.11.4 SB Models

12016500

248 MB500SB3-2318

12010000

128 MB500SB3-2316

707350

84 MB540SB2-2315

Interactive CPWProcessor CPW*

CPUs

L2 cache

per CPU

Chip Speed

MHz

Model

Table C.11.4.1 SB Models

* Note: The "Processor CPW" values listed for the SB models are identical to the

830-2403-1531 (8-way), the 840-2418-1540 (12-way) and the 840-2420-1540 (24-way).

However, due to the limited disk and memory of the SB models, it would not be possible

to measure these values using the CPW workload. Disk space is not a high priority for

middle-tier servers performing CPU-intensive work because they are always connected to

another computer acting as the "database" server in a multi-tier implementation.

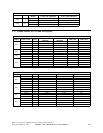

C.12 V4R4 Additions

The Model 7xx is new in V4R4. Also in V4R4 are the Model 170s features 2289 and 2388 were added.

See the chapter, AS/400 RISC Server Model Performance Behavior, for a description of the

performance highlights of these new models.

Testing in the Rochester laboratory has shown that for systems executing traditional commercial

applications such as RPG or COBOL interactive general business applications may experience about a

5% increase in CPU requirements. This effect was observed using the workload used to compute CPW, as

shown in the tables that follows. Except for systems which are nearing the need for an upgrade, we do not

expect this increase to significantly affect transaction response times. It is recommended that other

sections of the Performance Capabilities Reference Manual (or other sizing and positioning documents)

be used to estimate the impact of upgrading to the new release.

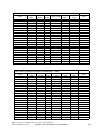

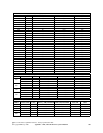

C.12.1 AS/400e Model 7xx Servers

MAX Interactive CPW = Interactive CPW (Knee) * 7/6

CPU % used by Interactive @ Knee = Interactive CPW (Knee) / Processor CPW * 100

CPU % used by Processor @ Knee = 100 - CPU % used by Interactive @ Knee

CPU % used by Interactive @ Max = Max Interactive CPW / Processor CPW * 100

280

2401600

44 MB255720-2064

(

1503

)

140

1201600

44 MB255720-2064

(

1502

)

40.8

351600

44 MB255720-2064

(

Base

)

653.3

560810

24 MB200720-2063

(

1504

)

280

240810

24 MB200720-2063

(

1503

)

140

120810

24 MB200720-2063

(

1502

)

40.8

35810

24 MB200720-2063 (Base)

280

240420

14 MB200720-2062 (1503)

140

120420

14 MB200720-2062 (1502)

81.7

70420

14 MB200720-2062 (1501)

40.8

35420

14 MB200720-2062 (Base)

140

120240

1n/a200720-2061 (1502)

81.7

70240

1n/a200720-2061 (1501)

40.8

35240

1n/a200720-2061 (Base)

Interactive CPW

(Max)

Interactive CPW

(Knee)

Processor CPW

CPUs

L2 cache

per CPU

Chip Speed

MHz

Model

Table C.12.1.1 Model 7xx Servers (all new Northstar models)

IBM i 6.1 Performance Capabilities Reference - January/April/October 2008

© Copyright IBM Corp. 2008 Appendix C CPW, CIW and MCU for System i Platform 361