Networking Silicon — 82540EP

Datasheet 5

2.0 Features of the 82540EP Gigabit Ethernet Controller

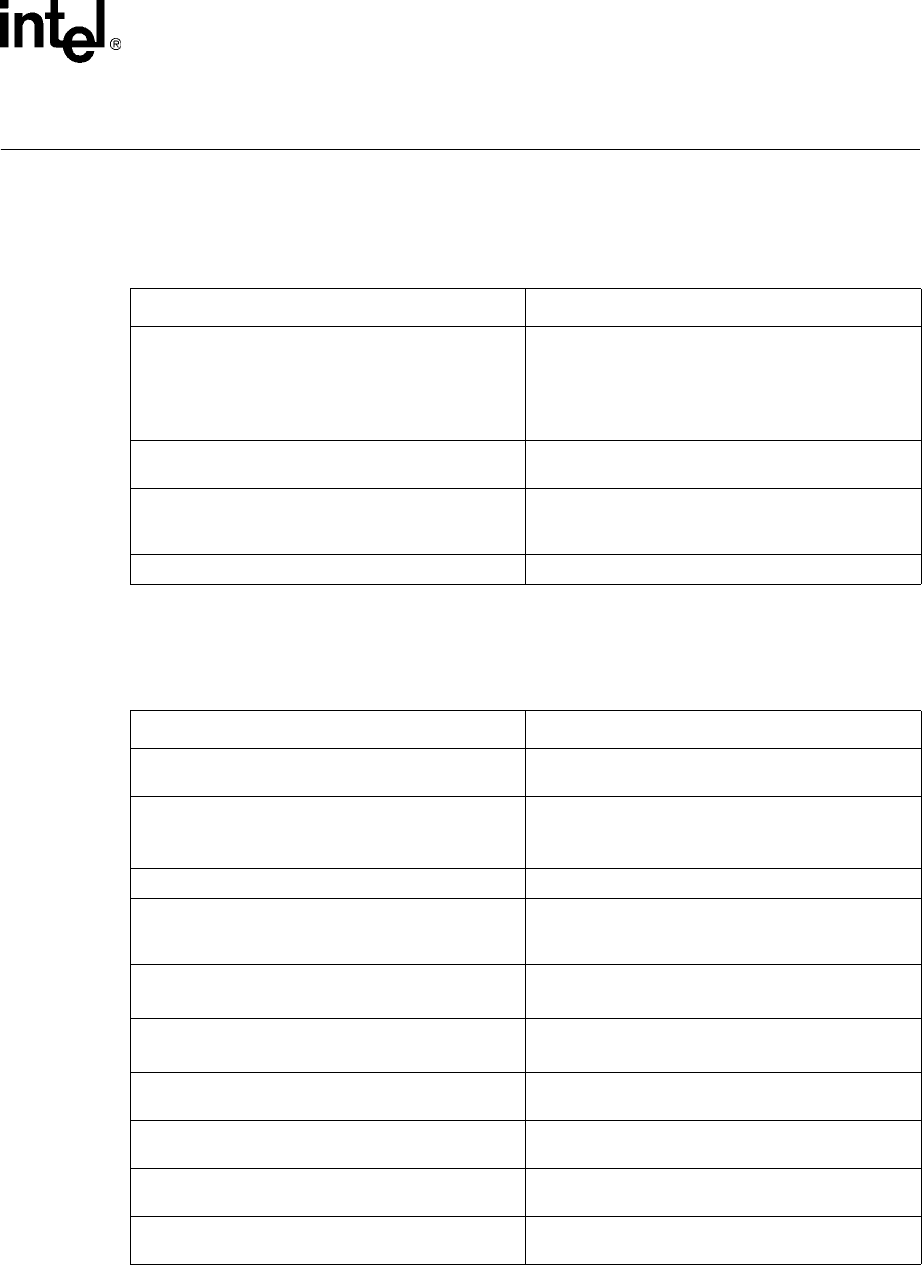

2.1 PCI Features

2.2 MAC Specific Features

Features Benefits

PCI Revision 2.3 support for 32-bit wide interface at

33 MHz and 66 MHz

• Application flexibility for LAN on Motherboard

(LOM) or embedded solutions

• 64-bit addressing for systems with more than 4

Gigabytes of physical memory

• Support for new PCI 2.3 interrupt status/control

Algorithms that optimally use advanced PCI, MWI,

MRM, and MRL commands

• Efficient bus operations

CardBus Information Services (CIS) Pointer

• Enables CardBus operation (when used with

external FLASH device and series termination on

PCI bus)

CLKRUN# Signal • PCI clock suspension for low power mobile design

Features Benefits

Low-latency transmit and receive queues

• Network packets handled without waiting or buffer

overflow.

IEEE 802.3x compliant flow control support with

software controllable pause times and threshold

values

• Control over the transmissions of pause frames

through software or hardware triggering

• Frame loss reduced from receive overruns

Caches up to 64 packet descriptors in a single burst • Efficient use of PCI bandwidth

Programmable host memory receive buffers (256

Bytes to 16 KBytes) and cache line size (16 Bytes to

256 Bytes)

• Efficient use of PCI bandwidth

Wide, optimized internal data path architecture

• Low latency data handling

• Superior DMA transfer rate performance

64 KByte configurable Transmit and Receive FIFO

buffers

• No external FIFO memory requirements

• FIFO size adjustable to application

Descriptor ring management hardware for transmit

and receive

• Simple software programming model

Optimized descriptor fetching and write-back

mechanisms

• Efficient system memory and use of PCI

bandwidth

Mechanism available for reducing interrupts

generated by transmit and receive operations

• Maximizes system performance and throughput

Support for transmission and reception of packets up

to 16 KBytes

• Enables jumbo frames