82540EP — Networking Silicon

8 Datasheet

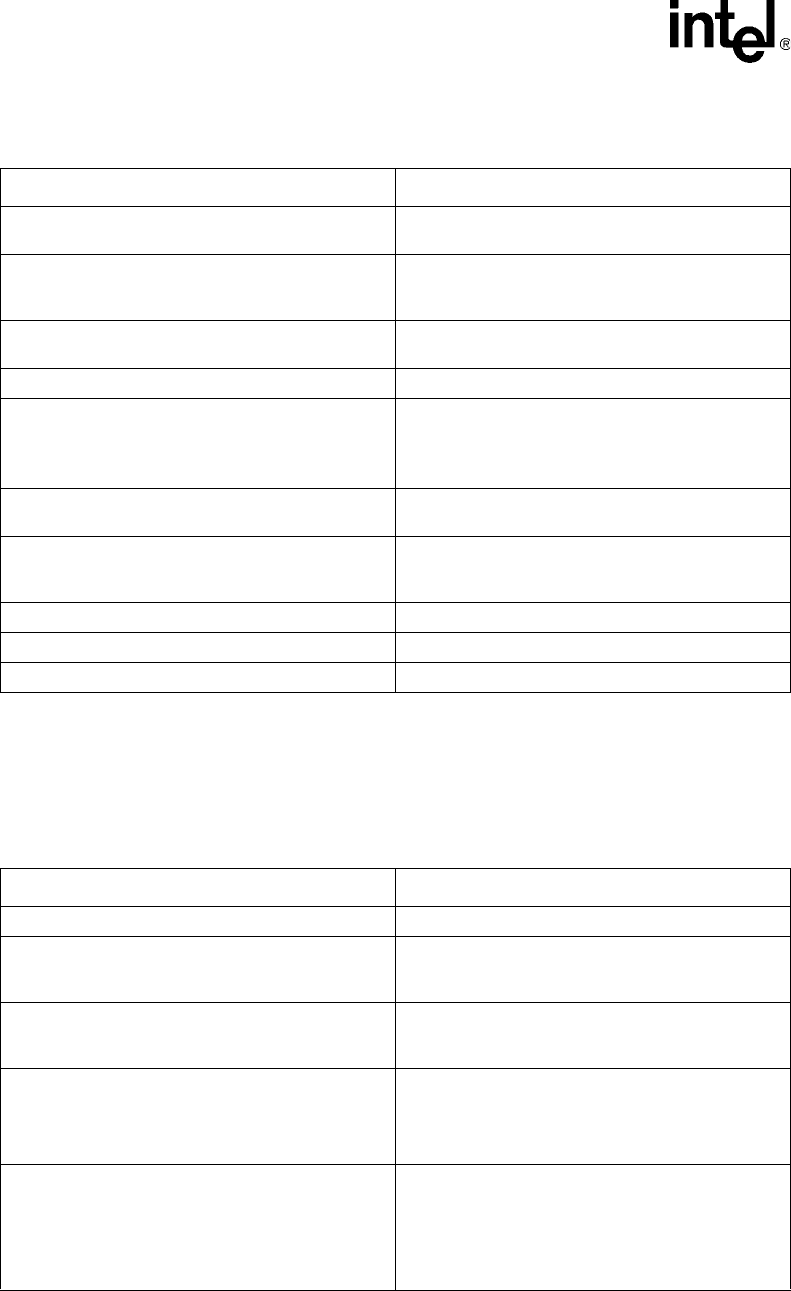

2.6 Additional Device Features

2.7 Technology Features

Features Benefits

Four activity and link indication outputs that directly

drive LEDs

• Link and activity indications (10, 100, and 1000

Mbps) on each port

Programmable LED functionality

• Software definable function (speed, link, and

activity) and blinking allowing flexible LED

implementations

Internal PLL for clock generation can use a 25 MHz

crystal

• Lower component count and system cost

JTAG (IEEE 1149.1) Test Access Port built in silicon • Simplified testing using boundary scan

On-chip power control circuitry

a

a. If applying the “low-power” EEPROM setting for the 82540EP chip, then only external voltage regulator circuits should be used

instead of the on-chip power control circuitry

• Reduced number of on-board power supply

regulators

• Simplified power supply design in less power-

critical applications

Four software definable pins

• Additional flexibility for LEDs or other low speed

I/O devices

Supports little endian byte ordering for both 32 and 64

bit systems and big endian byte ordering for 64 bit

systems

• Portable across application architectures

Two or three-pair cable downshift • Supports modular hardware accessories

Provides loopback capabilities • Validates silicon integrity

Minimal ballout change from the 82540EM • Pin Compatibility

Features Benefits

196-pin Ball Grid Array (TFBGA) package • 15 mm

2

component making LOM designs easier

Pin compatible with 82551QM and 82540EM

controllers

• Enables 10/100 Mbps Fast Ethernet or 1000 Mbps

Gigabit Ethernet implementations on the same

board with only minor stuffing option changes

Implemented in 0.15u CMOS process

• Offers lowest geometry to minimize power and

size while maintaining Intel quality reliability

standards

Operating temperature: 0

° C to 70° C (maximum)

operating temperature

Heat sink or forced airflow not required

65

° C to 140° C storage temperature range

• Simple thermal design

PCI Signaling: 3.3 V (5 V tolerant) PCI signaling

Typical targeted power dissipation:

• 1.38W @ D0 1000 Mb/s

• 386mW @ D3 100 Mb/s (wake-up enabled)

• <20mW @ D3 wake-up disabled

• Lower power requirements for mobile applications