124 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Physical Layer Interface

7.3 Intel 82555 Specific Registers

Note: The Intel MAC/PHY silicon devices (82558, 82559, 82550, and 82551) use the 82555 as the base

for their integrated PHY units. Therefore, the information contained in this section and the

following subsections apply to the all 8255x Fast Ethernet controllers except the 82557.

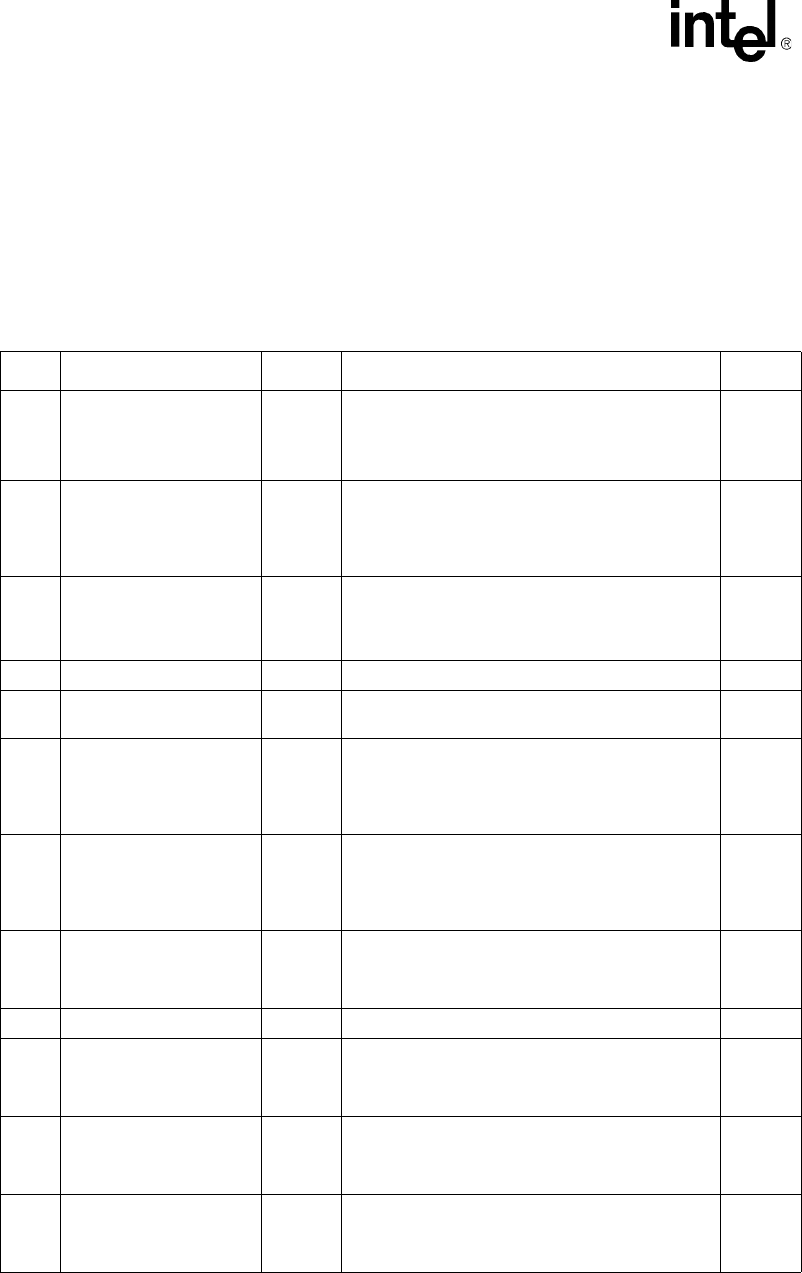

7.3.1 Status and Control Register: Register 16

Bit Name R / W Description Default

15 Flow Control RW

1 = Flow control enabled.

0 = Flow control disabled.

NOTE: This bit should always equal 0 for the

82559.

0

14 T4 Enable RW

This bit enable T4 when auto-negotiation is

disabled.

1 = Enable T4 technology

0 = Disable T4 technology

0

13 CRS Disconnect Control RW

This bit controls the RX100 CRS disconnect

function in repeater mode.

NOTE: This bit should always equal 0 for the

82559.

0 = DTE

1 = Rptr

12 Reserved This bit is reserved. 0

11

RCV De-Serializer In-

Sync Indication

RO

This bit is used as the 100BASE-TX RCV De-

Serializer In Sync Indication

0

10 100 Power Down RO

This bit provides 100BASE-T Power Down

Indication.

1 = Power down

0 = Normal operation

0

9 10 Power Down RO

This bit provides 10BASE-T Power Down

Indication.

1 = Power down

0 = Normal operation

0

8Polarity RO

This bit indicates 10BASE-T polarity.

1 = Reverse polarity

0 = Normal polarity

0

7:3 Reserved These bits are reserved. 0

2T4 RO

This bit is a result of the auto-negotiation process.

1 = 100BASE-T4.

0 = No 100BASE-T4

0

1 Speed RO

This bit is a result of the auto-negotiation process.

1 = 100 Mbps

0 = 10 Mbps

0

0 Duplex RO

This bit is a result of the auto-negotiation process.

1 = Full duplex

0 = Half duplex

0