62 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

The individual bit fields of the configure command is another area where there are numerous

differences between the controllers (82557, 82558, 82559, etc.). Therefore, a complete

configuration map for each device will be presented below. Bit descriptions for the configuration

bits follow the configuration map.

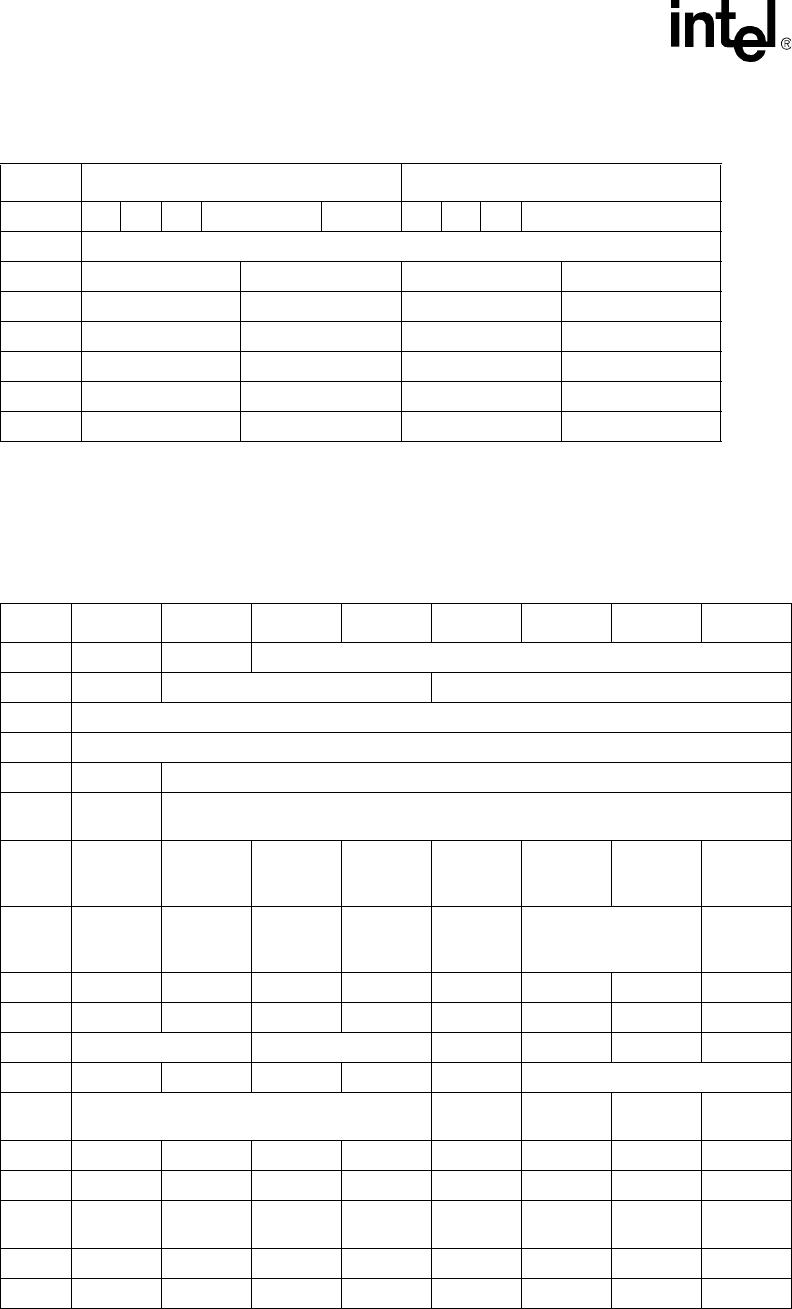

Figure 17. Configure Command Format

Offset Command Word Bits 31:16 Status Word Bits 15:0

00h EL S I 0000000000 010 C X OK XXXXXXXXXXXXX

04h Link Address (A31:A0)

08h Byte 3 Byte 2 Byte 1 Byte 0

0Ch Byte 7 Byte 6 Byte 5 Byte 4

10h Byte 11 Byte 10 Byte 9 Byte 8

14h Byte 15 Byte 14 Byte 13 Byte 12

18h Byte 19 Byte 18 Byte 17 Byte 16

1Ch 00 00 00 00 00 00 00 00 Byte 21 Byte 20

Table 38. 82557 Configuration Byte Map

Byte D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 Byte Count

1 0 Transmit FIFO Limit Receive FIFO Limit

2 Adaptive Interframe Spacing

3 Reserved (must be set to 0)

4 0 Receive DMA Maximum Byte Count

5

DMBC

Enable

Transmit DMA Maximum Byte Count

6

Save Bad

Frames

Discard

Overrun

Receive

11

CI

Interrupt

TNO

Interrupt

1 Late SCB

700000Underrun Retry

Discard

Short

Receive

80000000503/MII

900000000

10 Loopback Preamble Length NSAI 1 1 0

1100000Linear Priority

12 Interframe Spacing 0 0 0

L PRI

MODE

1300000000

1411110010

15

CRS and

CDT

10010

Broadcast

Disable

Promis-

cuous

1600000000

1701000000