32 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

• SCB Command Word. This register is where software writes commands for the CU and RU.

• SCB Status Word. The device places the CU and RU status for the CPU to read in this word.

• SCB General Pointer. The SCB General Pointer points to various data structures in main

memory depending on the current SCB Command word.

• Port Interface. This special interface allows the CPU to reset the device and force it to dump

information to main memory or perform an internal self test.

• EEPROM Control Register. The EEPROM Control Register allows the CPU to read and write

to an external EEPROM.

• MDI Control Register. This register allows the CPU to read and write information from

Physical Layer components through the Management Data Interface.

• Early Receive Interrupt Rx Byte Count (RXBC) Register. This register allows the CPU to read

the current value in the Receive DMA byte count register. The Receive DMA byte count

register tracks the number of receive data bytes that have been placed into host memory.

• Flow Control Threshold Register. This register allows the driver to set the flow control

threshold value. (This register is not included in the 82557.)

• Flow Control Command Register. This register allows the driver to indicate flow control

commands to the 82558 and later devices.

• Power Management Driver Register (PMDR). This register indicates power management

events to the driver.

The CSR can be accessed as either an I/O mapped or memory mapped PCI slave.

Note: The PCI Configuration space Base Address Registers (BARs) automatically request memory space

for the CSR and I/O space for the CSR. Software may use either memory mapped or I/O mapped

mode or even use them interchangeably. In most environments, memory mapped mode is the

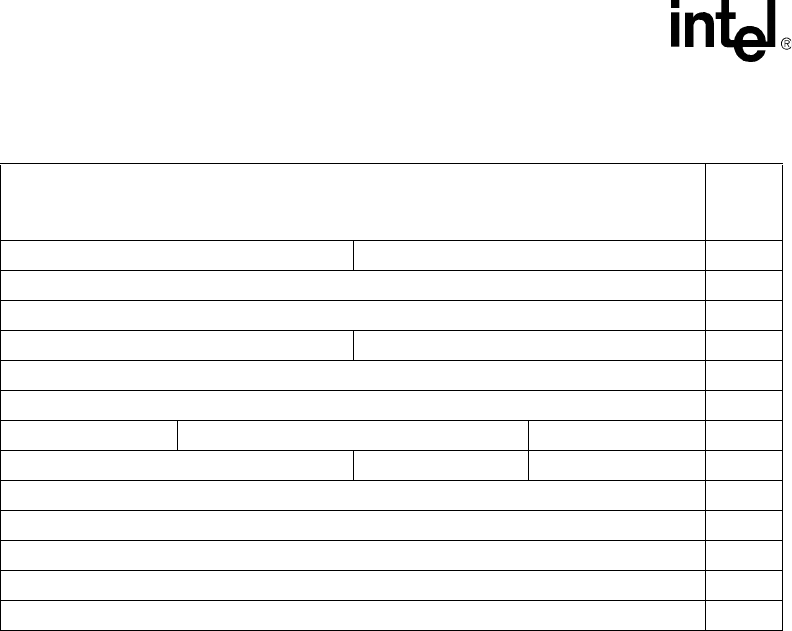

Table 11. Control / Status Register

Upper Word Lower Word Offset

31 16 15 0

SCB Command Word SCB Status Word 0h

SCB General Pointer 4h

PORT 8h

EEPROM Control Register Reserved Ch

MDI Control Register 10h

RX DMA Byte Count 14h

PMDR Flow Control Register Reserved 18h

Reserved General Status General Control 1Ch

Reserved 20h-2Ch

Function Event Register 30h

Function Event Mask Register 34h

Function Present State Register 38h

Force Event Register 3Ch