Datasheet 33

Networking Silicon — 82555

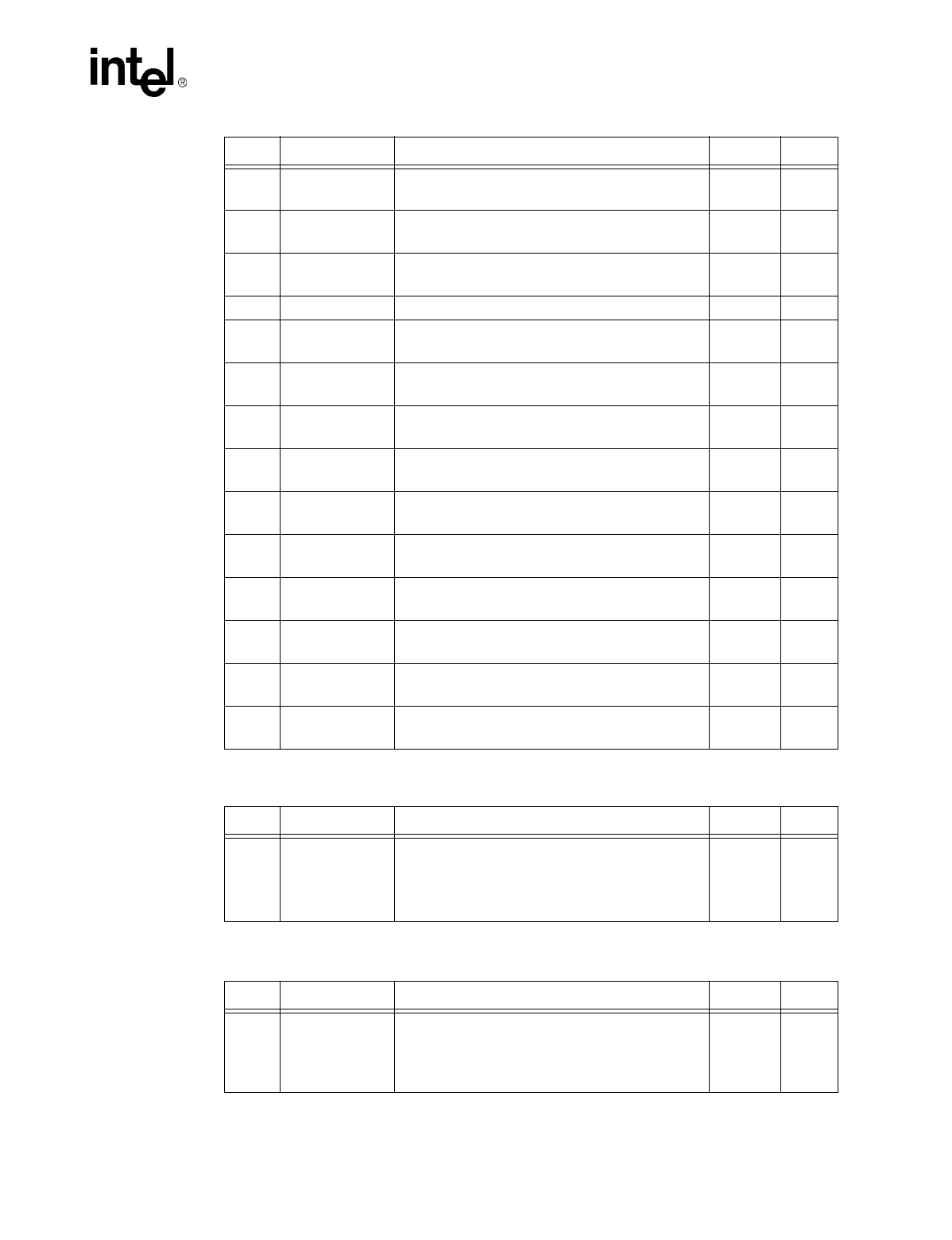

7.2.3.3 Register 20: 100BASE-TX Receive Disconnect Counter Bit Definitions

7.2.3.4 Register 21: 100BASE-TX Receive Error Frame Counter Bit Definitions

13 Force Transmit H-

Pattern

1 = Force transmit H-pattern

0 = Normal operation

0RW

12 Force 34 Transmit

Pattern

1 = Force 34 transmit pattern

0 = Normal operation

0RW

11 Good Link 1 = 100BASE-TX link good

0 = Normal operation

0RW

10 Reserved This bit is reserved and should be set to 0b. 0 RW

9 Transmit Carrier

Sense Disable

1 = Transmit Carrier Sense disabled

0 = Transmit Carrier Sense enabled

0RW

8 Disable Dynamic

Power-Down

1 = Dynamic Power-Down disabled

0 = Dynamic Power-Down enabled (normal)

0RW

7 Auto-Negotiation

Loopback

1 = Auto-Negotiation loopback

0 = Auto-Negotiation normal mode

0RW

6 MDI Tri-State 1 = MDI Tri-state (transmit driver tri-states)

0 = Normal operation

0RW

5 Filter By-pass 1 = By-pass filter

0 = Normal filter operation

0RW

4 Auto Polarity

Disable

1 = Auto Polarity disabled

0 = Normal polarity operation

0RW

3 Squelch Disable 1 = 10BASE-T squelch test disable

0 = Normal squelch operation

0RW

2 Extended

Squelch

1 = 10BASE-T Extended Squelch control enabled

0 = 10BASE-T Extended Squelch control disabled

-- RW

1 Link Integrity

Disable

1 = Link disabled

0 = Normal Link Integrity operation

0RW

0 Jabber Function

Disable

1 = Jabber disabled

0 = Normal Jabber operation

0RW

Bit(s) Name Description Default R/W

15:0 Disconnect Event This field contains a 16-bit counter that increments for

each disconnect event. The counter stops when full

(and does not roll over) and self-clears on read

In repeater mode, a frame that starts without “JK” is a

disconnect event.

-- RO

SC

Bit(s) Name Description Default R/W

15:0 Receive Error

Frame

This field contains a 16-bit counter that increments

once per frame for any receive error condition (such

as a symbol error or premature end of frame) in that

frame. The counter stops when full (and does not roll

over) and self-clears on read.

-- RO

SC

Bit(s) Name Description Default R/W