82555 — Networking Silicon

34

Datasheet

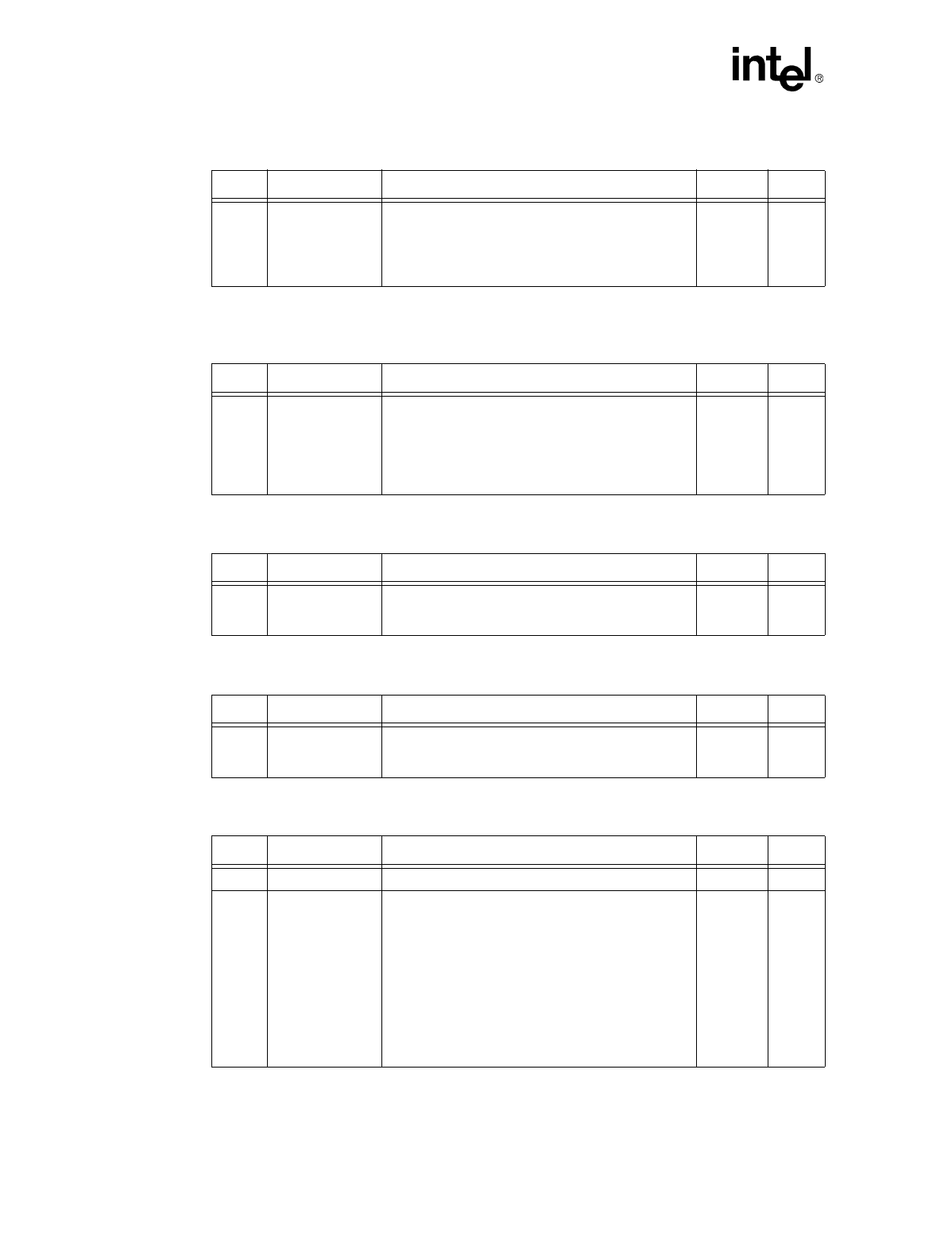

7.2.3.5 Register 22: Receive Symbol Error Counter Bit Definitions

7.2.3.6 Register 23: 100BASE-TX Receive Premature End of Frame Error Counter

Bit Definitions

7.2.3.7 Register 24: 10BASE-T Receive End of Frame Error Counter Bit Definitions

7.2.3.8 Register 25: 10BASE-T Transmit Jabber Detect Counter Bit Definitions

7.2.3.9 Register 27: 82555 Special Control Bit Definitions

Bit(s) Name Description Default R/W

15:0 Symbol Error

Counter

This field contains a 16-bit counter that increments for

each symbol error. The counter stops when full (and

does not roll over) and self-clears on read.

In a frame with a bad symbol, each sequential six bad

symbols count as one.

-- RO

SC

Bit(s) Name Description Default R/W

15:0 Premature End of

Frame

This field contains a 16-bit counter that increments for

each premature end of frame event. The counter

stops when full (and does not roll over) and self-clears

on read.

A frame without a “TR” at the end is considered a

premature end of frame event.

-- RO

SC

Bit(s) Name Description Default R/W

15:0 End of Frame

Counter

This is a 16-bit counter that increments for each end

of frame error event. The counter stops when full (and

does not roll over) and self-clears on read.

-- RO

SC

Bit(s) Name Description Default R/W

15:0 Jabber Detect

Counter

This is a 16-bit counter that increments for each

jabber detection event. The counter stops when full

(and does not roll over) and self-clears on read.

-- RO

SC

Bit(s) Name Description Default R/W

15:3 Reserved These bits are reserved and should be set to 0b. 0 RW

2:0 LED Switch

Control

Value

000

001

010

011

100

101

110

111

ACTLED

Activity

Speed

Speed

Activity

Off

Off

On

On

LILED

Link

Collision

Link

Collision

Off

On

Off

On

000 RW