22 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

PCI Interface

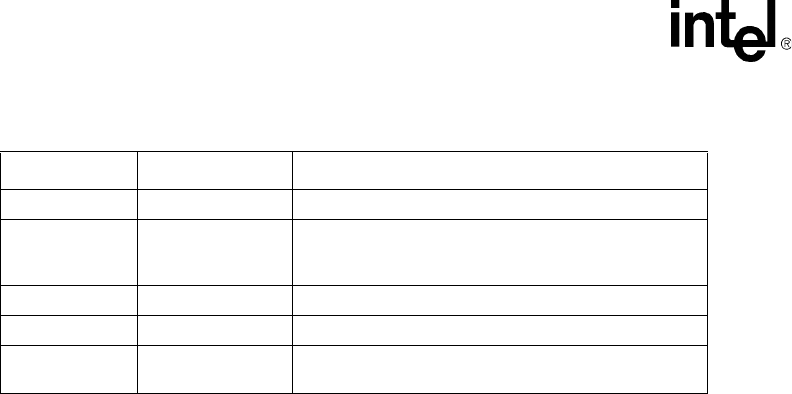

Table 7. Generated PCI Commands

The controllers do not generate I/O commands, Interrupt Acknowledge cycles, or Configuration

cycles. The controllers also do not support Dual Address Cycle (DAC). Targets (typically the

system bridge) must respond to all of the commands that the Ethernet controller generates.

4.2.1 Memory Write and Invalidate

The 82558, 82559, 82550, and 82551 have 4 internal DMA channels. Of these 4, the Receive DMA

channel is used to deposit packet data received from the link into system memory. The Receive

DMA channel uses both the Memory Write (MW) and the Memory Write and Invalidate (MWI)

commands. In order to use MWI the device must guarantee:

• A minimum transfer of one cache line.

• All byte-enable bits are active during each MWI access.

• The device may cross a cache line boundary only if it intends to transfer the entire next cache

line too.

In order to ensure the above conditions, the device may use the MWI command only if the

following conditions hold:

1. The cache line size written in the CLS register during PCI configuration is 8 or 16 Dwords.

2. The accessed address is cache line aligned.

3. The 82558 or 82559 has at least a cache line size of data byte in its Receive FIFO.

4. There is at least a cache line size of space left in the system memory buffer. In addition, the

device will use two configuration bits to enable and disable the use of MWI:

a. MWI Enable bit in the PCI Configuration Command register (Section 4.1, “PCI

Configuration Space”).

b. MWI Enable bit in the device Configure command (Section 6.4.2.3, “Configure (010b)”).

If any one of these conditions does not hold, the device uses the MW command. If a MWI cycle is

started and one of the conditions does not hold any more (for example, the data space in the

memory buffer is less than the CLS), then the device terminates the MWI cycle at the end of the

cache line. The next cycle is a MWI or MW cycle according to the conditions listed above.

If a MWI cycle is terminated by a Retry from the target, the device attempts to retry the access

using the MWI command. If a MWI cycle is terminated in the middle of a cache line by a

disconnect from the target (including Disconnect-C), the device issues a new cycle from the

disconnected point using the MW command. If the disconnect occurs on a cache line boundary, the

PCI Command Name Circumstance Used

0x6 MR TxCB “S” bit read.

0x7 MW

CB and RFD. Writing statistics counters or dump data

buffer to memory. Writing received packet data into

receive buffers.

0xC MRM Reading transmit data buffers.

0xE MRL CB, TBD, and RFD.

0xF

MWI (82558 &

82559)

Writing received packet data into receive buffers.