52 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

to increase performance by decreasing NOS receive latencies. However, most software early

interrupt schemes would increase CPU utilization and software complexity. Thus, use of this

register is not recommended.

Bits 13:11 of this register are reserved and should equal 0. Bits 10:3 contain the receive DMA byte

count. Bits 2:0 are hard wired to 0, giving an 8-byte granularity.

The RXBC register is first initialized to the size of the next receive data buffer. This data buffer

size could equal the HDS size (if header RFDs are used) or the RFD buffer size. When a frame is

received over the wire and passed to memory by the receive DMA, the register decrements until it

reaches zero. At this point the register is set to the size of the next receive data buffer (HDS or

RFD), and the receive DMA is restarted.

6.3.7 Early Receive Interrupt

Note: For operating systems with an increased interrupt latencies, the Early Receive Interrupt feature can

be used to mask some of the latency. However, for Linux or Unix operating systems, the Early

Receive Interrupt does not provide any benefit since these operating systems have little interrupt

latencies. Thus, there is essentially no use for this feature in Linux or Unix operating systems.

The Early Receive Interrupt register is an 8-bit field at offset 18h of the CSR. This register is not

present on the 82557. It is used for configuring the device to assert an additional receive interrupt

before the entire packet has been received and deposited into host memory.

When operating with the Early Receive Interrupt scheme, the device generates an early interrupt

depending on the length of the frame. When a frame is received, the controller looks at the Type/

Length field (byte 13 and 14) of the received frame. If the Type/Length field contains a valid length

value (0 < Type/Length ≤ 1500), the device generates an early interrupt approximately X quad-

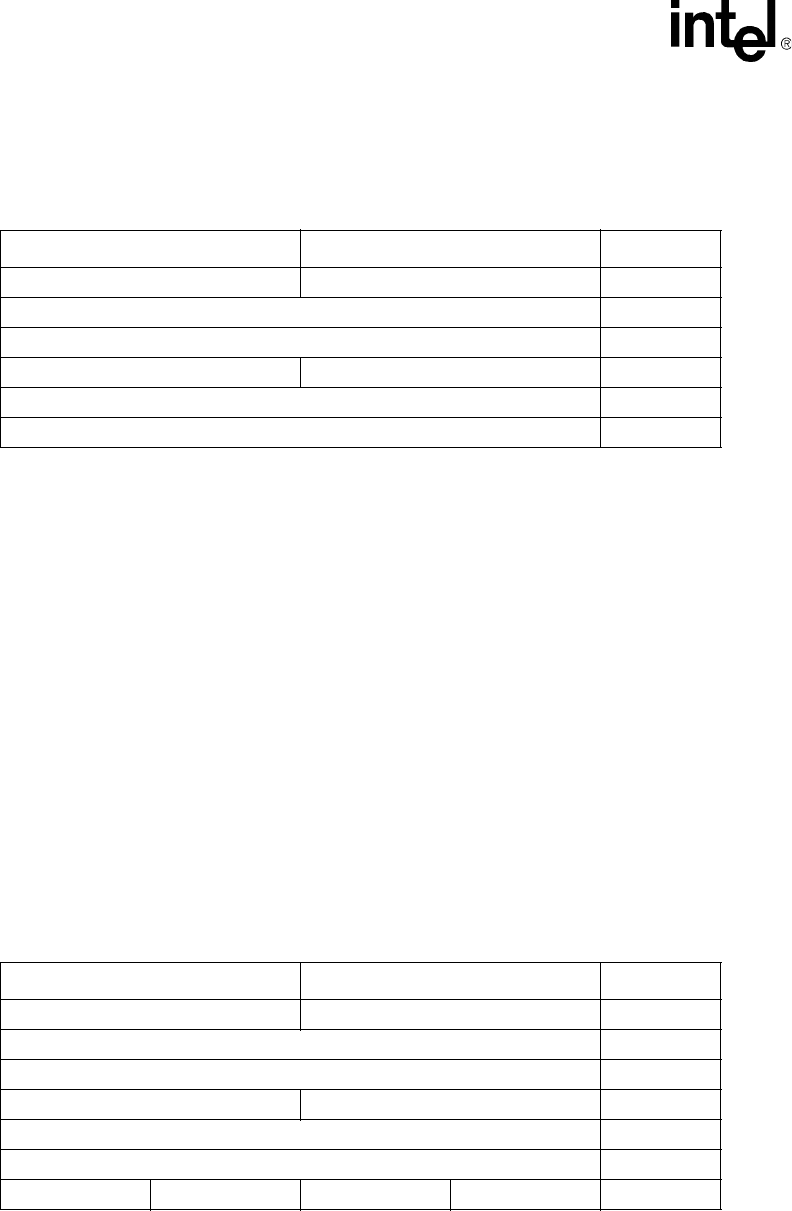

Table 27. Receive Byte Count Register Location

Upper Word (D31:D16) Lower Word (D15:D0) Offset

SCB Command Word SCB Status Word Base + 0h

SCB General Pointer Base + 4h

PORT Base + 8h

EEPROM Control Register Reserved Base + Ch

MDI Control Register Base + 10h

Early Receive Interrupt Receive Byte Count Register Base + 14h

Table 28. Early Receive Interrupt Register Location

Upper Word (D31:D16) Lower Word (D15:D0) Offset

SCB Command Word SCB Status Word Base + 0h

SCB General Pointer Base + 4h

PORT Base + 8h

EEPROM Control Register Reserved Base + Ch

MDI Control Register Base + 10h

Early Receive Interrupt Receive Byte Count Register Base + 14h

PMDR FC Xon/Xoff FC Threshold Early Rx Int Base + 18h