46 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

The serial EEPROM or equivalent integrated circuit (IC) stores configuration data for the

controller and the adapter. The EEPROM is a serial in and serial out device. Serial EEPROMs

range in size from 16 to 256 registers of 16 bits per register. All accesses, read or write, are

preceded by a command instruction to the device. The command instructions begin with a logical 1

as the start bit, two opcode bits (indicating read, write, erase, etc.), and n-bits of address. The

address field varies with the size of the EEPROM and is 6 bits for a 64 register EEPROM and 8 bits

for a 256 register device. The end of the address field is indicated by a dummy 0 bit from the

EEPROM, which indicates the entire address field has been transferred to the device. A command

is issued by asserting the chip select signal and clocking the data into the EEPROM on its data

input pin relative to the serial clock input. The chip select signal is de-asserted after the completion

of the EEPROM cycle (command, address and data).

6.3.4.1 CPU Accesses to the EEPROM

The EEPROM access port is shown below. This register is located at offset 0Eh in the device

Control register block. The CPU directly manipulates these bits to read to or write from the

EEPROM. There should be no other local bus activity at this time.

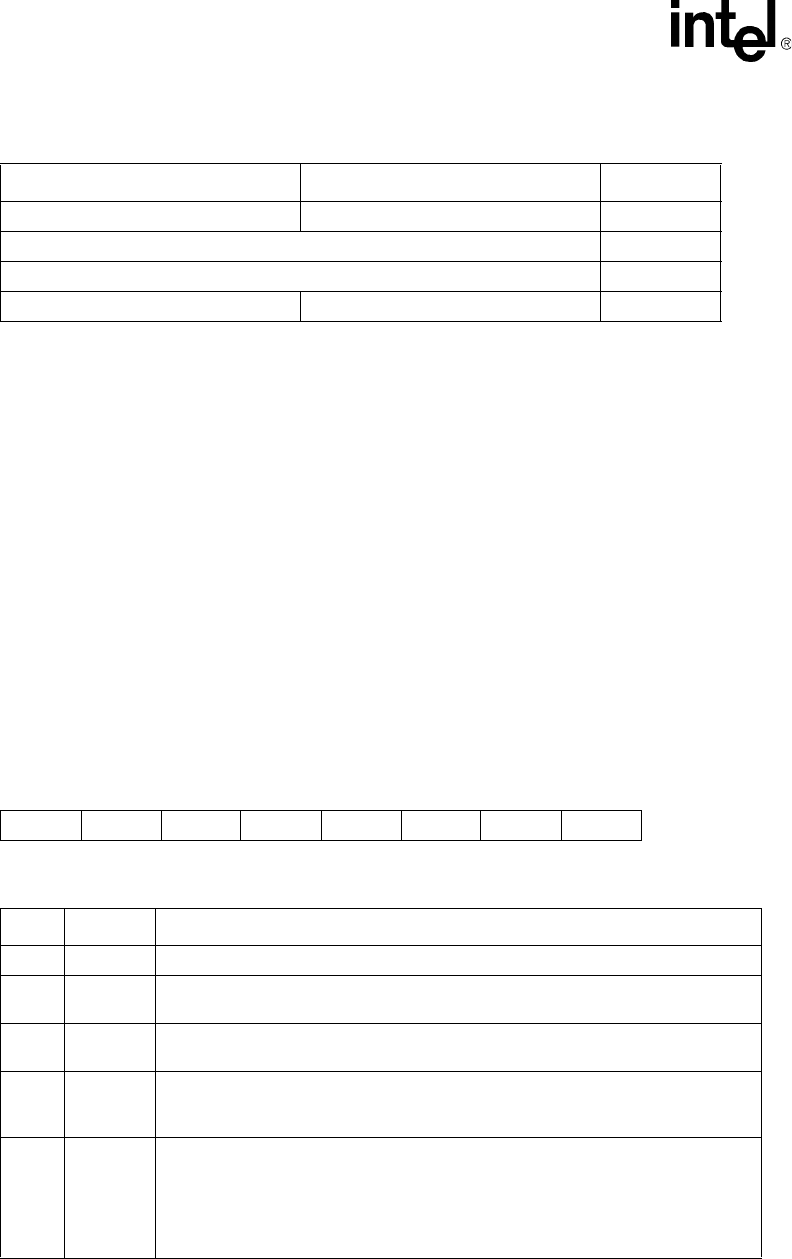

Table 21. EEPROM Control Register Locations

Upper Word (D31:D16) Lower Word (D15:D0) Offset

SCB Command Word SCB Status Word Base + 0h

SCB General Pointer Base + 4h

PORT Base + 8h

EEPROM Control Register Reserved Base + Ch

Figure 12. EEPROM Control Register

23 22 21 20 19 18 17 16

X X X X EEDO EEDI EECS EESK

Table 22. EEPROM Control Register Bits Definitions

Bit Symbol Description

23:20 Reserved.

19 EEDO

Serial Data Out. This bit contains the value read from the EEPROM when

performing a read operation on the EEPROM.

18 EEDI

Serial Data In. The value of this bit is written to the EEPROM when performing

write operations.

17 EECS

Chip Select. Setting this bit to 1 enables the EEPROM. Setting the bit to 0 disables

the EEPROM. This bit must be set to 0 for a minimum of 1 µs between consecutive

instruction cycles.

16 EESK

Serial Clock. Setting this bit to 1 drives the serial clock line to the EEPROM high.

Setting this bit to 0 drives the serial clock line low. Toggling this bit high and then low

clocks data in or out of the EEPROM. The serial EEPROM specifies a minimum

clock period of 4 µs. The minimum period that the clock can be high or low is 1 µs. If

the clock is driven high for only 1 µs, then it must followed by a low period of 3 µs to

meet the minimum clock frequency specification.