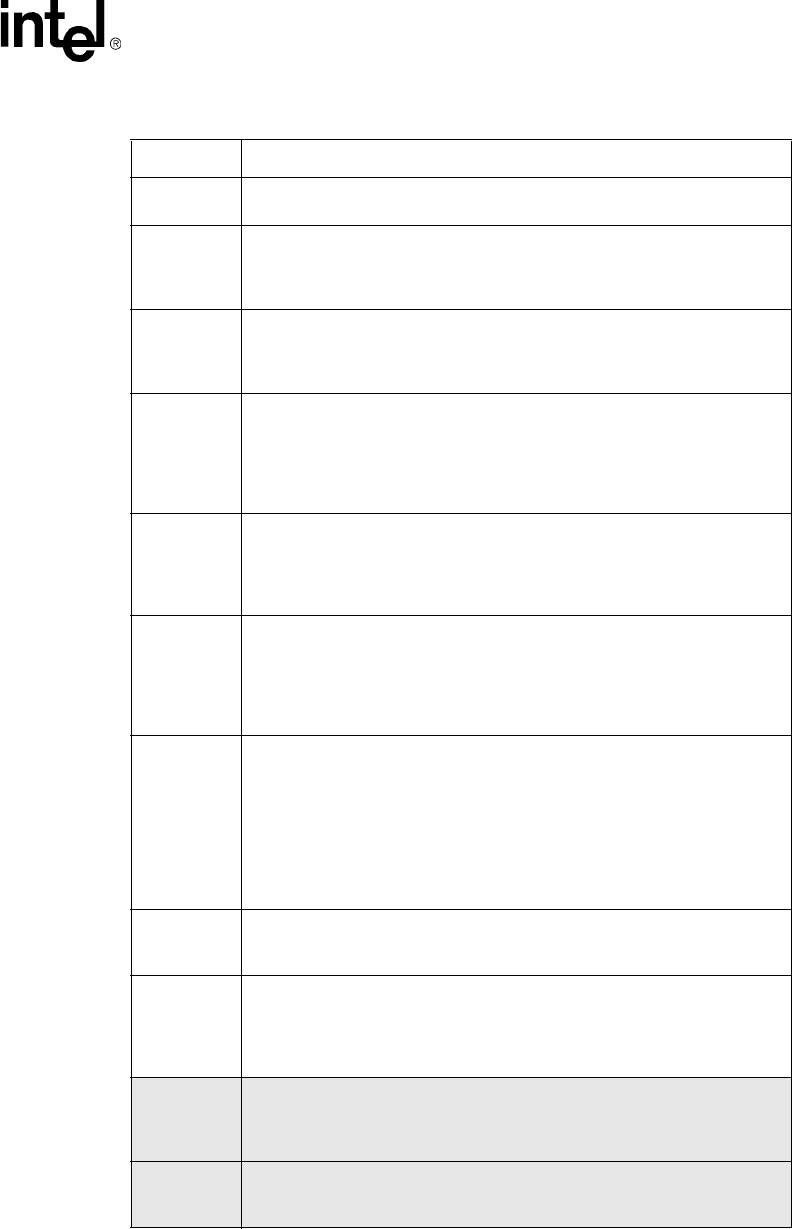

Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual 41

Host Software Interface

28

Transmit multiple collisions. This counter contains the number of

transmitted frames that encountered more than one collision.

32

Transmit total collisions. This counter contains the total number of

collisions that were encountered while attempting to transmit. This count

includes late collisions and collisions from frames that encountered

maximum collisions.

36

Receive good frames. This counter contains the number of frames that

were received properly from the link. It is updated only after the actual

reception from the link is completed and all data bytes are stored in

memory.

40

Receive CRC errors. This counter contains the number of aligned frames

discarded out to a CRC error. This counter is updated, if needed, regardless

of the RU state. If the RX_ER pin is asserted during a receive frame, this

counter is incremented (only once per receive frame). This counter is

counter is mutually exclusive to the alignment errors and short frames

counters.

44

Receive alignment errors. This counter contains the number of frames

that are both misaligned (in other words, CRS de-asserts on a non-octet

boundary) and contain a CRC error. The counter is updated, if needed,

regardless of the RU state. This counter is mutually exclusive to the CRC

errors and short frames counters.

48

Receive resource errors. This counter contains the number of good

frames discarded due to unavailable resources. Frames intended for a host

whose RU is in the no resources state fall into this category. If the device is

configured to save bad frames and the status of the received frame

indicates that it is a bad frame, this counter is not updated unless the RU is

in a no resources state.

52

Receive overrun errors. This counter contains the number of frames

known to be lost because the internal receive FIFO overflowed (also known

as receive overrun). This can occur if the device is unable to get the

necessary bandwidth on the PCI (system) bus. If the overflow condition

persists for more than one frame, the frames that follow the first can also be

lost. However, since a lost frame indicator does not exist, these lost frames

may not be counted. A frame that was counted as an overrun will not be

counted in other error counters (short frames, CRC errors, or alignment

errors).

56

Receive collision detect (CDT) errors. This counter contains the number

of frames that encountered collisions during frame reception. This counter is

always 0 on the 82559.

60

Receive short frame errors. This counter contains the number of received

frames that are shorter than the minimum frame length. It is mutually

exclusive to the CRC errors and alignment errors counters and has a higher

priority (in other words, a short frame will always increment only the short

frames counter).

64

Flow control transmit pause. This counter contains the number of flow

control frames transmitted by the device. The count includes both the XOFF

frames transmitted and XON frames (in other words, PAUSE(0))

transmitted.

68

Flow control receive pause. This counter contains the number of flow

control frames received by the device. It includes both the XOFF frames

received and XON frames (PAUSE(0)) received.

Table 17. Statistical Counters

Byte Offset Device Statistic