34 Board Manual

Intel

®

IQ80321 I/O Processor Evaluation Platform

Hardware Reference Section

3.4 Memory Subsystem

Memory subsystem consists of the SDRAM as well as the Flash memory subsystems.

3.4.1 DDR SDRAM

The DDR SDRAM interface consists of a 64-bit wide data path to support 1.6 GB/sec throughput. An

8-bit Error Correction Code (ECC) is stored into the DDR SDRAM array along with the data and is

checked when the data is read.

3.4.1.1 Battery Backup

Battery backup is provided to save any information in DDR during a power failure. The evaluation

board contains a Li-ion battery, a charging circuit and a regulator circuit.

DDR technology provides enabling data preservation through the self-refresh command. When the

processor receives an active Primary PCI-X reset, the self-refresh command issues, driving SCKE

signals low. Upon seeing this condition, the board logic circuit holds SCKE low before the processor

loses power. Batteries maintain power to DDR and logic, to ensure self-refresh mode. When the

circuit detects PRST# returning to inactive state, the circuit releases the hold on SCKE. Removing the

battery can disable the battery circuit. When the battery remains in the platform when it is de-powered

and/or removed from the chassis, the battery maintains DDR for about four hours. Once power is

reapplied, the battery is fully charged.

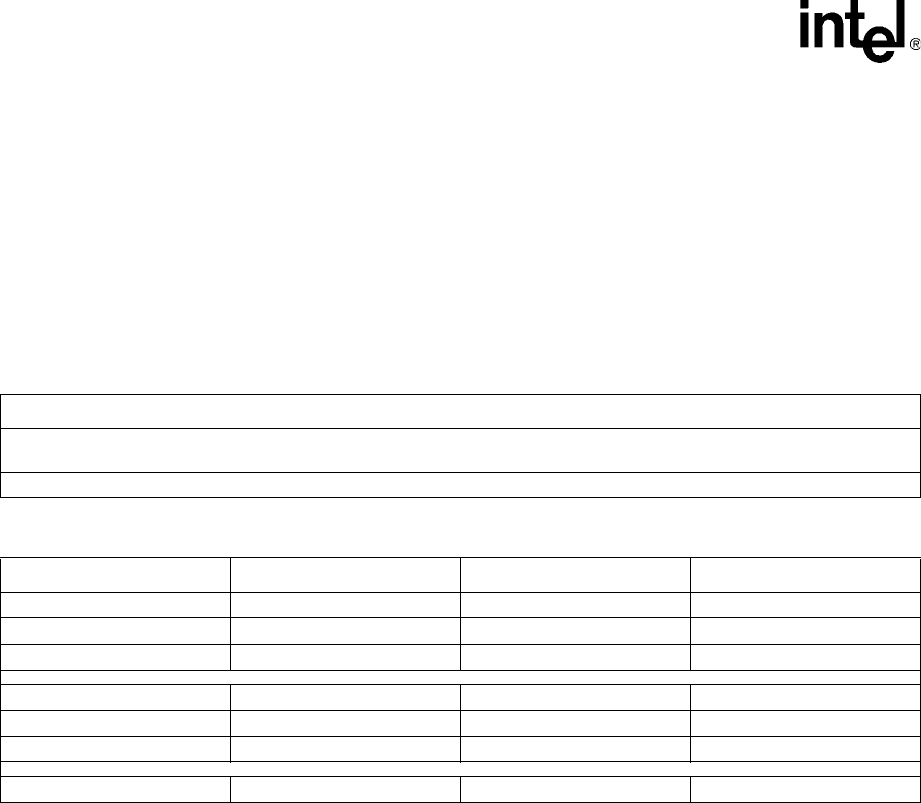

Table 8. DDR Memory Features

Description

The board features two banks of DDR SDRAM in the form of one two-bank dual inline memory module (DIMM), only Un-buffered

PC1600 DIMMs.

The Intel

®

IQ80321 Evaluation Platform Board has a single DIMM connector supporting the DIMM arrangements listed in Table 9.

Table 9. Supported DIMM Types

Type Size Type Size

DDR200 (PC1600) 8MX64 CL2DIMM (64 MB)

DDR200 16MX64 CL2 DIMM (128 MB)

DDR200 32MX64 CL2 DIMM (256 MB)

DDR200 8MX72 CL2 ECC DIMM (64 MB)

DDR200 16MX72 CL2 ECC DIMM (128 MB)

DDR200 32MX72 CL2 ECC DIMM (256 MB)

DDR200 (1 GB)