66 Board Manual

Intel

®

IQ80321 I/O Processor Evaluation Platform

Hardware Reference Section

3.10.9.19 Jumper J1G2

3.10.9.20 Jumper J3E1

3.10.9.21 Jumper J3G1

Initialization Device Select:

Used as a chip select during configuration read and write transactions on the secondary bus.

Applications that do not require access to the bridge configuration registers from the

secondary bus pull this pin low.

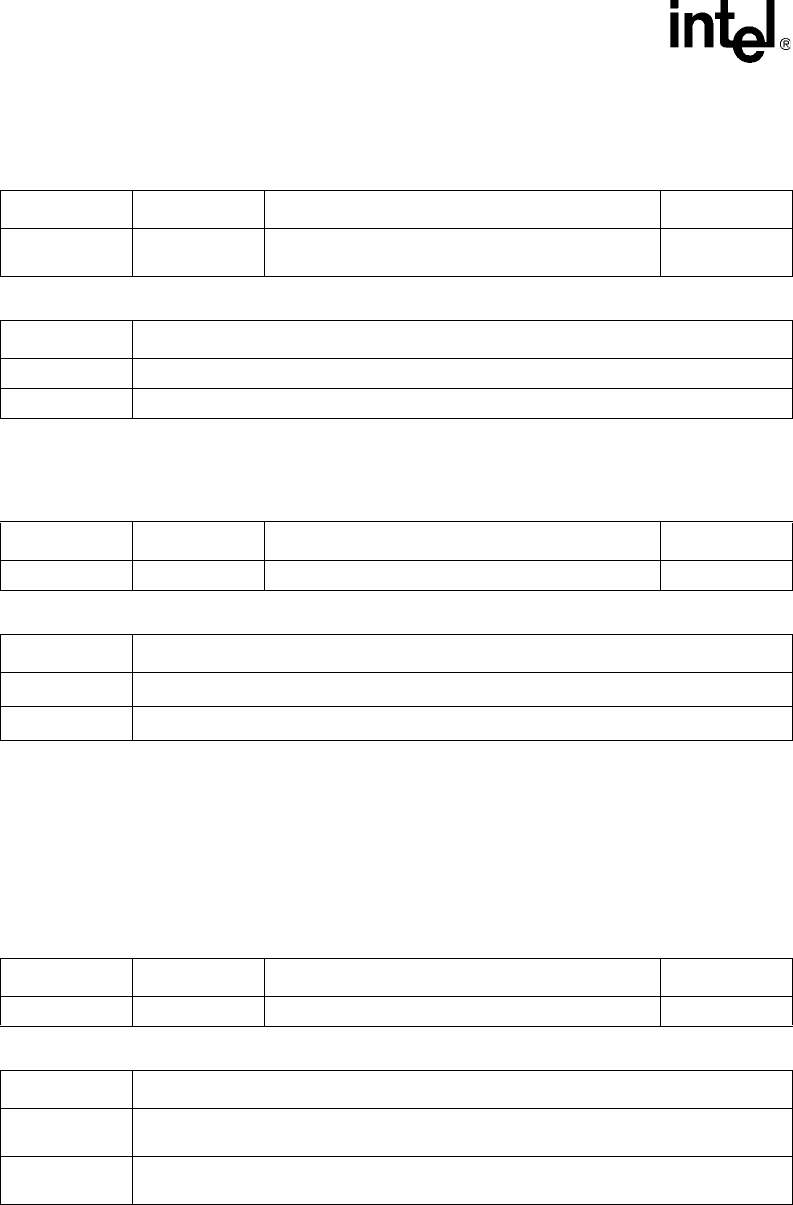

Table 76. Jumper J1G2: Descriptions

Jumper Association Description Factory Default

J1G2 PPCI-X Reset

Can isolated the PCI-X reset from getting to the

board.

2-3

Table 77. Jumper J1G2: Settings and Operation Mode

J1G2 Operation Mode

Pins 1,2 P_RST (primary side reset) disconnected from reset circuitry.

Pins 2,3 P_RST (primary side reset) used to reset board.

Table 78. Jumper J3E1: Descriptions

Jumper Association Description Factory Default

J3E1 SPCI-X Clock Enables spread-spectrum on the SPCI-X clock. 2-3

Table 79. Jumper J3E1: Settings and Operation Mode

J3E1 Operation Mode

Pins 1,2

Spread-spectrum enabled.

Pins 2,3

Spread-spectrum disabled.

Table 80. Jumper J3G1: Descriptions

Jumper Association Description Factory Default

J3G1 PCI-X Bridge S_IDSEL: Enables Bridge access from the SPCI-X side. 2-3

Table 81. Jumper J3G1: Settings and Operation Mode

J3G1 Operation Mode

Pins 1,2

Uses S_IDSEL as chip select during configuration read and write transactions on the

secondary bus.

Pins 2,3

S_IDSEL is pulled down for application that do not require access to bridge configuration

registers from secondary bus.