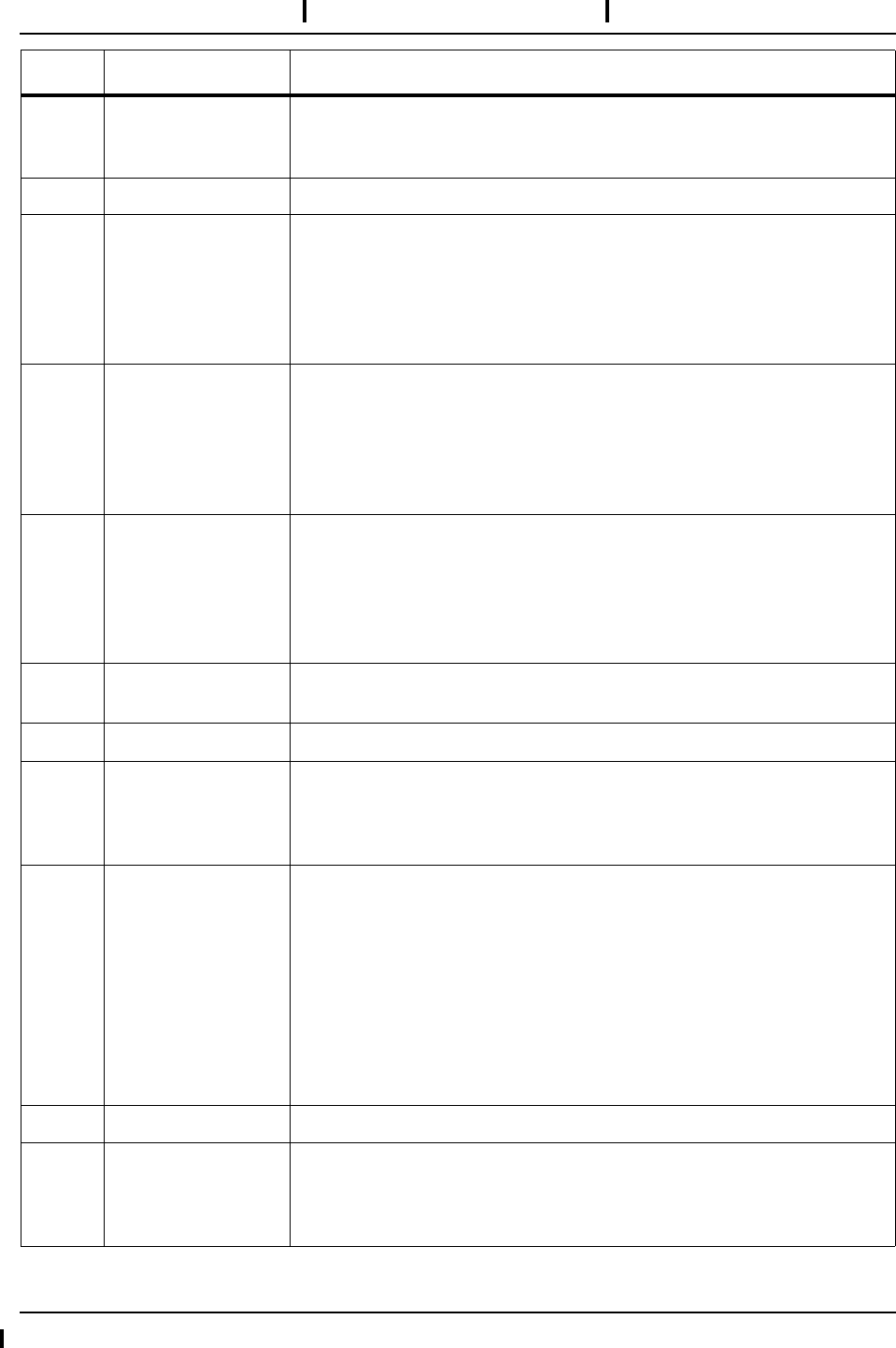

70

Sundance Technology ST201 PRELIMINARY draft 2

15 DMAHaltBusy This read-only bit indicates that a DMA Halt operation (TxDMAHalt or

RxDMAHalt) is in progress and the drivers should wait for this bit to be

cleared before performing other actions.

16 Reserved Reserved for future use. Should be set to 0.

17 RxEarlyEnable This read/write bit determines when the ST201 may start RxDMA a

receive frame. By default (cleared), RxDMA qualify for bus-master arbi-

tration when the frame becomes visible, normally at 60 bytes unless a

RxEarlyThresh threshold smaller than that has been set. When set to

one, RxDMA won’t start until the RxEarlyThresh threshold has been

crossed (or the frame completes, whichever is first).

18 CountdownSpeed This read/write bit sets the speed at which Countdown counts. When

CountdownSpeed is cleared, the count rate is once every 3.2 us (i.e. 4

byte times at 10 Mbps). When CountdownSpeed is set, the count rate

is once every 320 ns (i.e. 4 byte times at 100 Mbps). By setting appro-

priate CountdownSpeed for the wire speed, conversions can be made

between byte times and counter values using simple shift operations.

19 CountdownMode This read/write bit controls the operating mode of the Countdown regis-

ter. With this bit cleared, Countdown begins its down counting opera-

tion as soon as a non-zero value is written to it. With this bit set,

Countdown will not begin counting down until TxDMAComplete (in

IntStatus) is set. See the Countdown register definition for more infor-

mation on the Countdown modes.

20 MWIDisable Setting this read/write bit prevents the bus master logic from using the

Memory Write Invalidate (MWI) PCI command.

21 Reserved Reserved for future use. Should be set to 0.

22 RxDMAOverrun-

Frame

This read/write bit, when clear (the default), causes the RxDMA engine

to discard receive overrun frames without transferring them to system

memory. When this bit is set, the RxDMA engine keeps and transfers

overrun frames.

23 CountdownIntEna-

ble

This read-only bit specifies whether expiration of Countdown can gen-

erate interrupts. If CountdownIntEnable is clear, Countdown expiration

will not set IntRequested; if it is set, expiration of Countdown will set

IntRequested. CountdownIntEnable is managed completely by the

hardware. This bit is cleared automatically by the act of setting IntRe-

quested or when a zero value is written into Countdown. This bit is set

implicitly when a non-zero value is written into Countdown by the host.

This allows the host to write a non-zero value to Countdown and an

interrupt will be generated in a corresponding amount of time. By writ-

ing a zero value to Countdown the host can suppress interrupts.

29..24 Reserved Reserved for future use. Should be set to 0.

30 TargetAbort This read-only bit is set when the ST201 experiences a target abort

sequence when operating as a bus master. This bit indicates a fatal

error, and must be cleared before further TxDMA or RxDMA operation

can proceed. This bit is cleared by the GlobalReset/DMA bit.

BIT BIT NAME BIT DESCRIPTION