www.ti.com

6.13C6xxxSpecificDMARulesandGuidelines

6.13.1CacheCoherencyIssuesforAlgorithmProducers

Y

X = 0ld

Y = new

X

L2 cache External memory

DMA

X

Y

X = 0ld

Y = new

X

L2 cache External memory

Y

DMA

C6xxxSpecificDMARulesandGuidelines

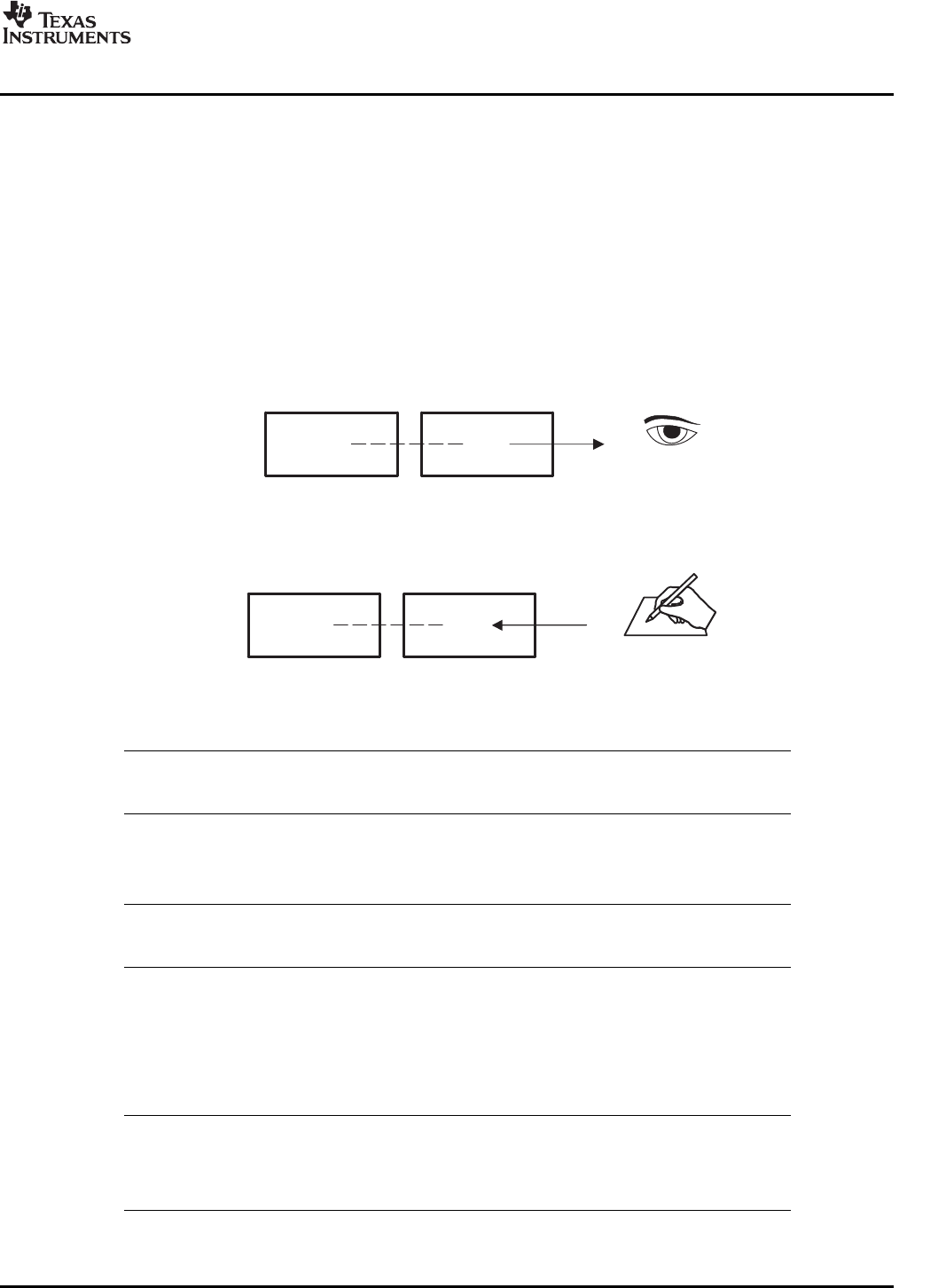

IncertainC6000targets,datathatareinbothexternalmemoryandtheL2cachecancausecoherence

problemswithbackgroundDMAtransfersinseveralways.Thefiguresbelowdepictsomememoryaccess

scenariosthatpotentiallyleadtoproblems.Welaterintroducerulesandguidelinesforbothalgorithmand

frameworkdeveloperstoensurecorrectoperationofC6000algorithms.

InSection6.13.2,CPUaccessofthememorycorrespondingtolocationxbringsitintotheL2cache.

SubsequentwritestoxtakeplaceintheL2cacheuntilthecachelinecontainingxgetswrittenbackto

externalmemory.IfaDMAtransferstartscopyingthedatafromlocationxtoanotherlocation,itmayend

upreadingstalevalueofxinexternalmemorysincecertainDMAcontrollerswillnotdetectpresenceor

flushingofadirtycachelinecontainingx.Toavoidthisproblem,thecachemustbeflushedbeforethe

DMAreadproceeds.

InSection6.13.3,thelocationxhasbeenbroughtintotheL2cache.SupposeaDMAtransferwritesnew

datatolocationx.Inthiscase,theCPUwouldaccesstheoldcacheddatainasubsequentread,unless

thecachedcopyisinvalidated.

Algorithmsmustenforcecoherenceandalignment/sizeconstraintsforinternalbufferstheyrequest

throughtheIALGinterface.Todealwiththesecoherencyproblems,thefollowingnewguidelinesand

ruleshavebeenadded.

DMAGuideline3

Toensurecorrectness,AllC6000algorithmsthatimplementIDMA2needtobesuppliedwiththe

internalmemorytheyrequestfromtheclientapplicationusingalgAlloc().

Thisguidelineappliestotheclientapplication,ratherthantothealgorithm.IfDMAGuideline3isfollowed;

i.e.,ifthetypeofmemoryrequestedisprovided,thealgorithmisguaranteedtooperatecorrectly.

DMARule6

C6000algorithmsmustnotissueanyCPUread/writestobuffersinexternalmemorythatareinvolved

inDMAtransfers.Thisalsoappliestobufferspassedtothealgorithmthroughitsalgorithminterface.

DMARule6isnecessarybecauseitistheonlywayforaneXpressDSP-compliantalgorithmtoavoid

havingtodealwithcachecoherenceoperationssuchascachelinewriteback,cachelineinvalidate,etc.

Theseoperationsarelow-levelandshouldbedealtwithattheclientapplicationlevel.Withthe

introductionofDMARule6,noexternalbuffersinvolvedinDMAtransferswillendupinthecache,and

thereforenoexternalcoherencyproblemswilloccur.

DMARule7

IfaC6000algorithmhasimplementedtheIDMA2interface,theclientmustallocatealltherequired

externalmemoryatacachelineboundary.Thesebuffersmustbeamultipleofcachelinelengthin

size.Theclientmustalsoensurethatthesebuffersarenotincachebeforepassingthemtothe

algorithm.

SPRU352G–June2005–RevisedFebruary2007UseoftheDMAResource69

SubmitDocumentationFeedback