www.ti.com

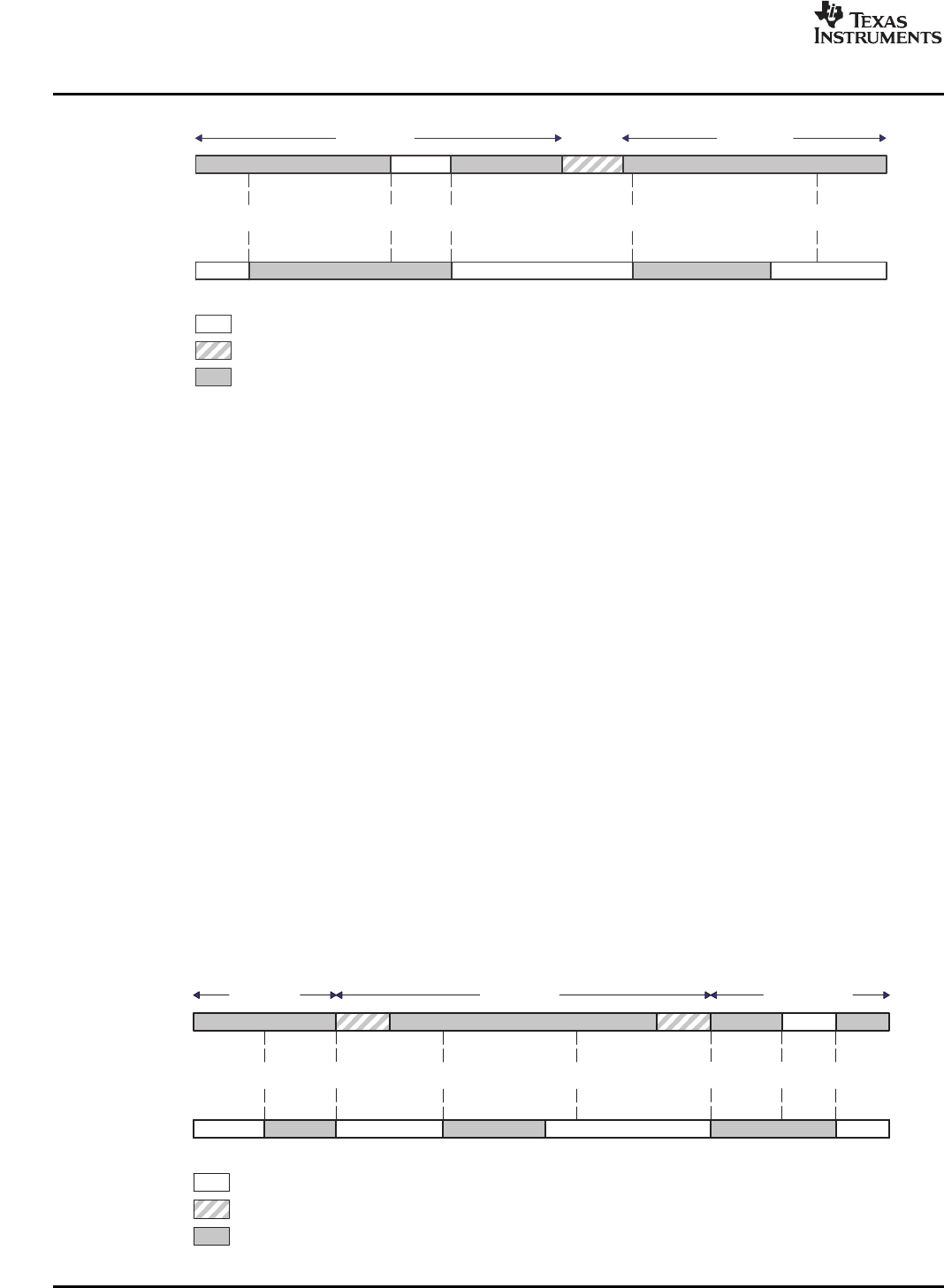

DMA/CPU idle

CPU context switch

CPU/DMA active

Algorithm A

active

Algorithm B

active

CPU context

(timeline)

DMA context

(timeline)

1 2 3 4 5

6.15.3PreemptiveSystem

DMA/CPU idle

CPU context switch

CPU/DMA activ

Algorithm A

active

Algorithm B

active

active

Algorithm A

CPU context

(timeline)

DMA context

(timeline)

1 2 3 4 5 6 7

Inter-AlgorithmSynchronization

Events

1.AlgorithmArequestsadatatransferbycallingACPY2_start().Theframeworkexecutesthisrequest

immediatelysincetheDMAchannelisfree.

2.AlgorithmAcallsACPY2_wait()towaitforthedatatransfertocomplete.Theframeworkcheckstosee

thatthedataarestillbeingtransferred.

3.ThedatatransferiscompleteandtheframeworkreturnscontroltoAlgorithmAsoitcanprocessthe

transferreddata.

4.AlgorithmBrequestsadatatransferbycallingACPY2_start().Theframeworkexecutesthisrequest

immediatelysincetheDMAchannelisfree.

5.AlgorithmBcallsACPY2_complete()tocheckifthedatatransferhascompleted.Theframework

checkstoseethatthedatahasbeentransferred.AlgorithmBcanprocessthetransferreddata.

NoticethatalgorithmAmustwaitforthetransfertocompletebecausetheparallelCPUprocessingtakes

lesstimethanthedatatransfer,whereasalgorithmB'sdatatransferhascompletedatthetimeof

synchronization.

Insummary,wecanseefromSection6.15.2thatsharingaphysicalDMAchannelbetweenseveral

algorithmsistrivialaslongasthealgorithmsdon'tpreempteachother.

SharingaphysicalDMAchannelamongtwoalgorithmsinapreemptivesystemrequiressomeprocedure

tomanagethesharedresource.Thesystemmusthaveapolicyforhandlingthesituationwhereone

algorithmpreemptsanotheralgorithmwhilethesharedphysicalDMAchanneliscurrentlybeingused.

Let'sassumethattheframeworkpreemptsalgorithmAinordertorunalgorithmB.

•Scenario1:ThesystempolicyistoabortthecurrentDMAtransfertofree-uptheDMAdevicetothe

higherpriorityalgorithm.SeeSection6.15.4.

Thesystem'spolicyistoabortthecurrentDMAtransferwhencontextswitchingtoahigherpriority

72UseoftheDMAResourceSPRU352G–June2005–RevisedFebruary2007

SubmitDocumentationFeedback