PCI v3.0.151 Getting Started Guide www.xilinx.com 23

UG157 August 31, 2005

Design Support

R

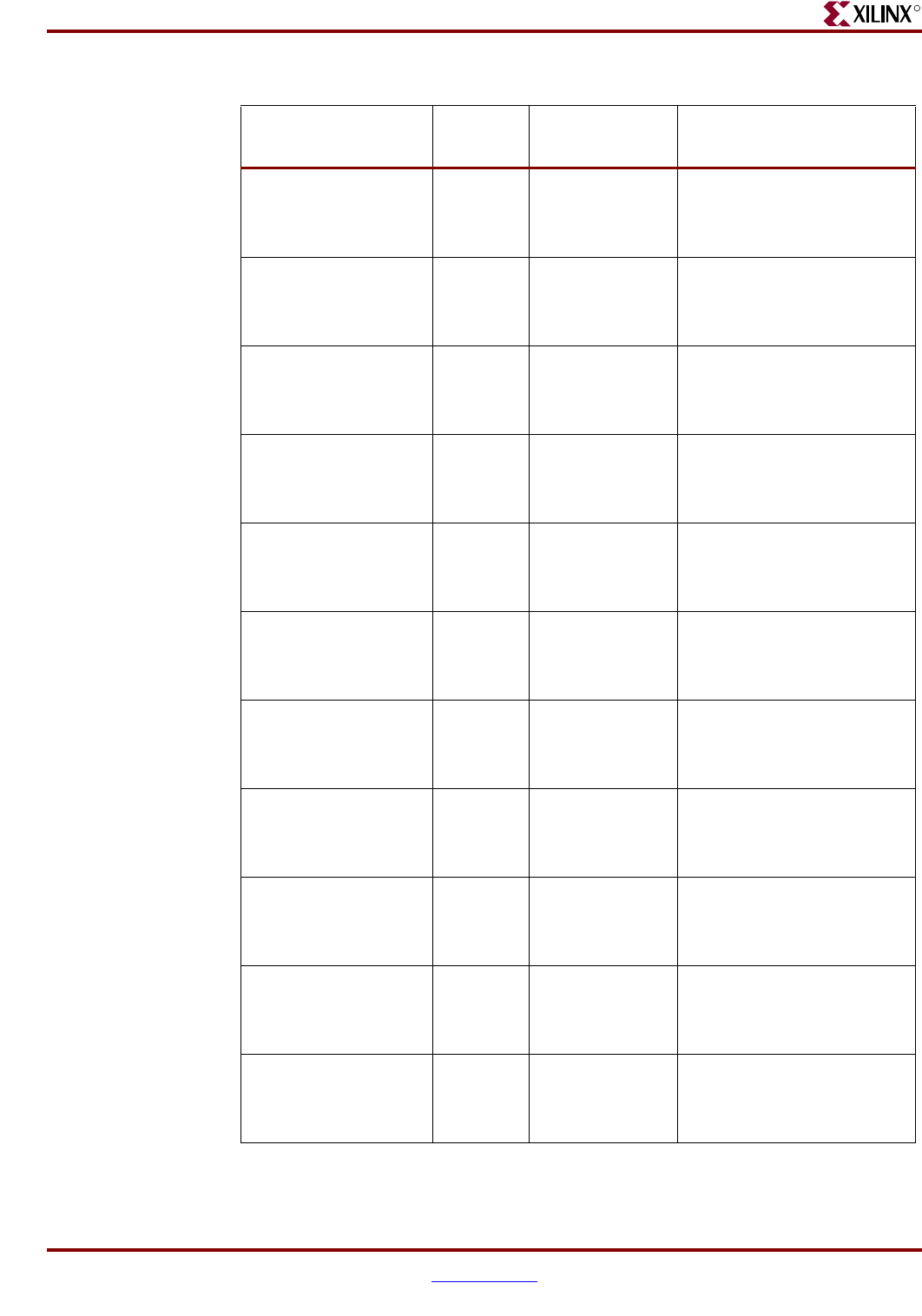

4VSX35-FF668-10C/I

global clock

33 MHz

3.3V

64-bit

pcim_lc_33_3_g 4vsx35ff668_64_33g.ucf

no guide file

4VFX20-FF672-10C/I

global clock

33 MHz

3.3V

64-bit

pcim_lc_33_3_g 4vfx20ff672_64_33g.ucf

no guide file

4VLX25-FF668-10C/I

regional clock

33 MHz

3.3V

64-bit

pcim_lc_33_3_r 4vlx25ff668_64_33r.ucf

no guide file

4VSX35-FF668-10C/I

regional clock

33 MHz

3.3V

64-bit

pcim_lc_33_3_r 4vsx35ff668_64_33r.ucf

no guide file

4VFX20-FF672-10C/I

regional clock

33 MHz

3.3V

64-bit

pcim_lc_33_3_r 4vfx20ff672_64_33r.ucf

no guide file

4VLX25-FF668-11C/I

regional clock

66 MHz

3.3V

64-bit

pcim_lc_66_3_r 4vlx25ff668_64_66r.ucf

no guide file

4VSX35-FF668-11C/I

regional clock

66 MHz

3.3V

64-bit

pcim_lc_66_3_r 4vsx35ff668_64_66r.ucf

no guide file

4VFX20-FF672-11C/I

regional clock

66 MHz

3.3V

64-bit

pcim_lc_66_3_r 4vlx20ff672_64_66r.ucf

no guide file

2S30-PQ208-5C 33 MHz

5.0V

32-bit

pcim_lc_33_5_s 2s030pq208_32_33.ucf

no guide file

2S30-PQ208-5C 33 MHz

3.3V

32-bit

pcim_lc_33_3_s 2s030pq208_32_33.ucf

no guide file

2S50-PQ208-5C 33 MHz

5.0V

32-bit

pcim_lc_33_5_s 2s050pq208_32_33.ucf

no guide file

Table 3-1: Device and Interface Selection Table (Continued)

Supported

Device

Bus

Type

Wrapper File

Constraints File/

Guide File