34 www.xilinx.com PCI v3.0.151 Getting Started Guide

UG157 August 31, 2005

Chapter 3: Family Specific Considerations

R

Bus Clock Usage

The bus clock output provided by the interface is derived from the bus clock input, and is

distributed using a global clock buffer. The interface itself is fully synchronous to this

clock. In general, the portion of the user application that communicates with the interface

must also be synchronous to this clock.

It is important to note that the frequency of this clock is not guaranteed to be constant. In

fact, in a compliant system, the clock may be any frequency, up to and including the

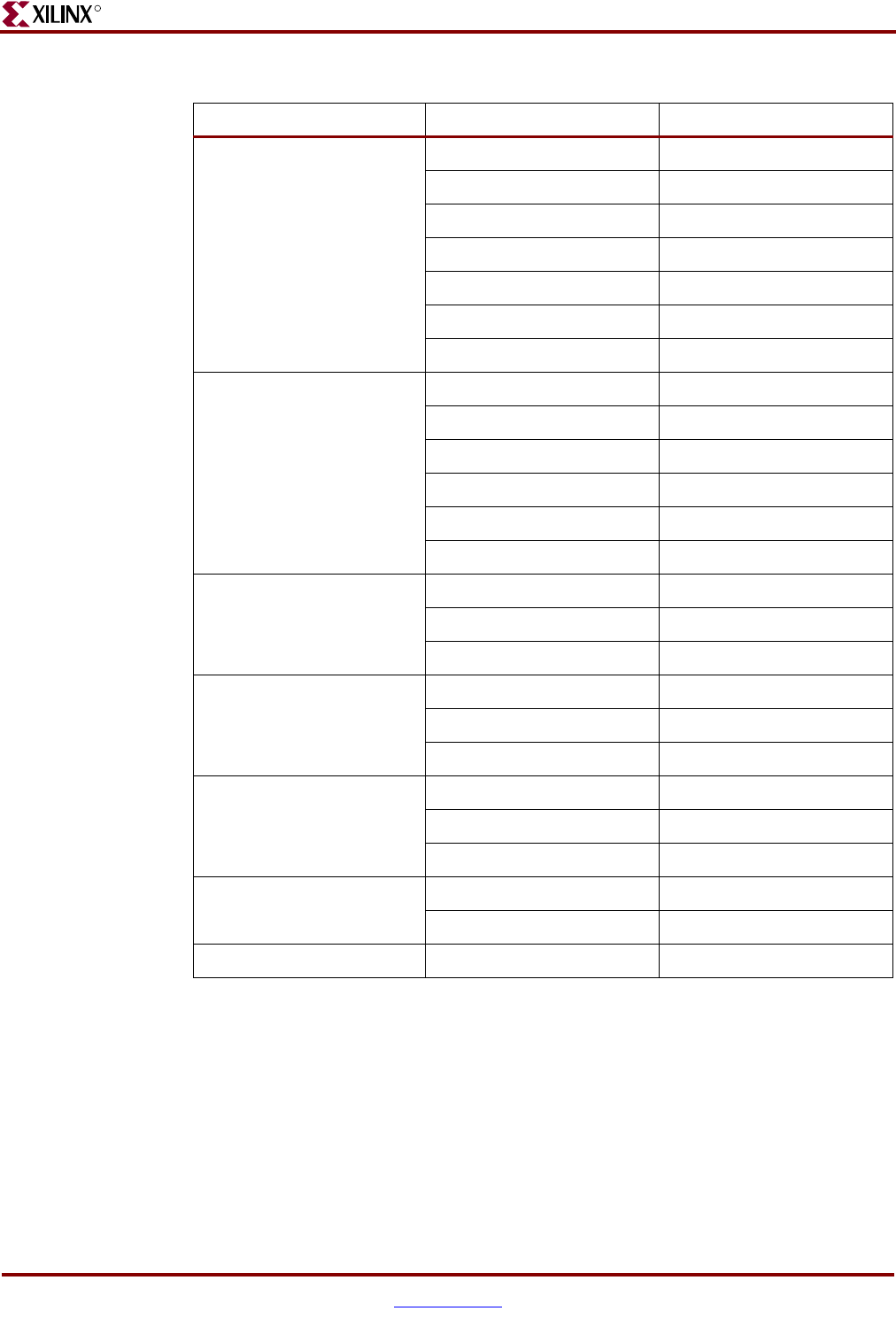

FF668

LX15 2

LX25 4

LX40 2

LX60 2

FX12 2

SX25 2

SX35 4

FF1148

LX40 4

LX60 4

LX80 6

LX100 6

LX160 6

SX55 4

FF1513

LX100 8

LX160 8

LX200 8

FF672

FX20 2

FX40 none

FX60 none

FF1152

FX40 4

FX60 4

FX100 4

FF1517

FX100 6

FX140 6

FF1760 FX140 8

Table 3-4: Virtex-4 Device and Package 64-bit Interfaces

Package Device 64-bit Interfaces