SP605 Hardware User Guide www.xilinx.com 19

UG526 (v1.1.1) February 1, 2010

Detailed Description

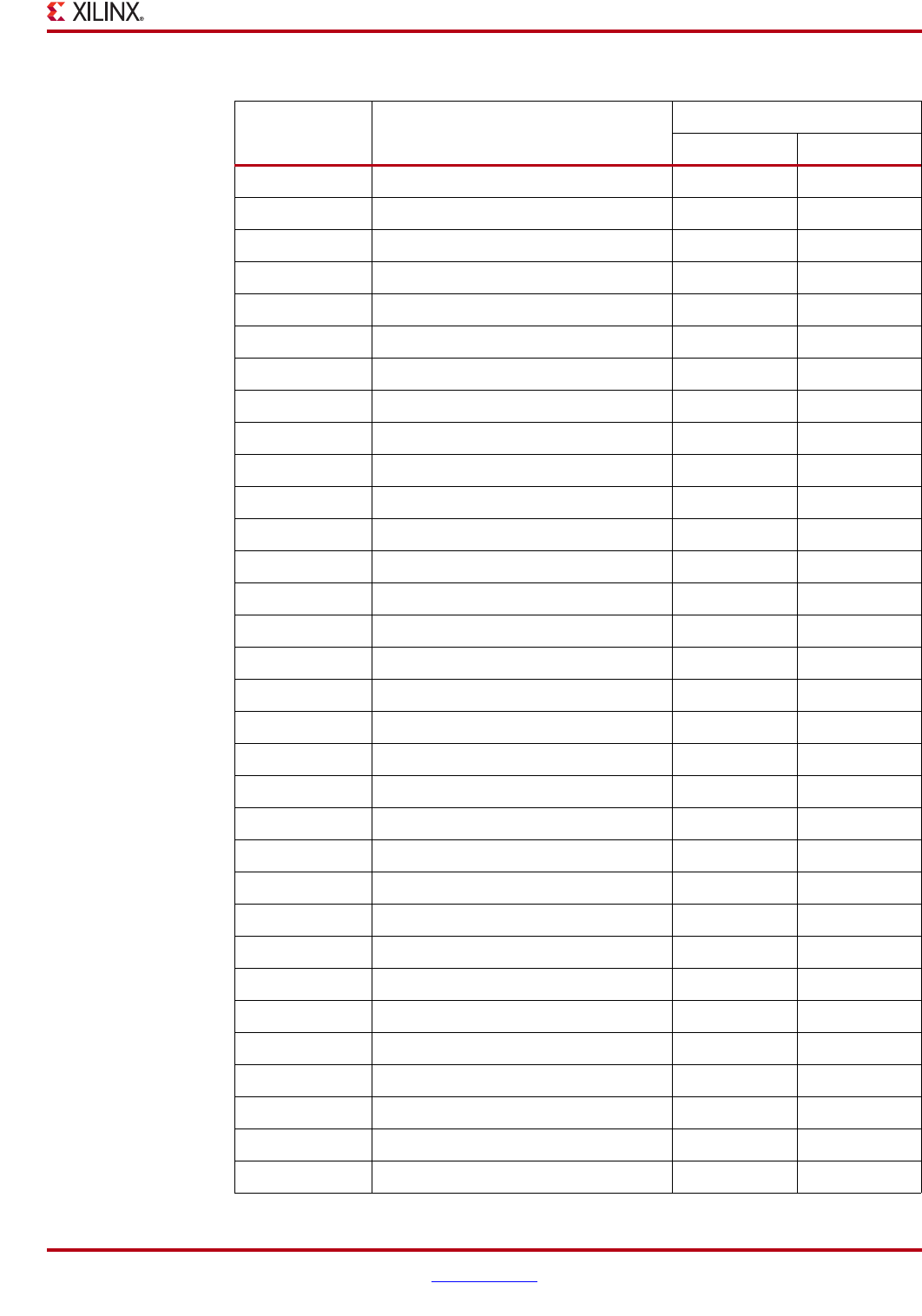

E22 FLASH_A16 55 A17

E20 FLASH_A17 18 A18

F22 FLASH_A18 17 A19

F21 FLASH_A19 16 A20

H19 FLASH_A20 11 A21

H18 FLASH_A21 10 A22

F20 FLASH_A22 9 A23

G19 FLASH_A23 26 A24

AA20 FPGA_D0_DIN_MISO_MISO1 34 DQ0

R13 FPGA_D1_MISO2 36 DQ1

T14 FPGA_D2_MISO3 39 DQ2

AA6 FLASH_D3 41 DQ3

AB6 FLASH_D4 47 DQ4

Y5 FLASH_D5 49 DQ5

AB5 FLASH_D6 51 DQ6

W9 FLASH_D7 53 DQ7

T7 FLASH_D8 35 DQ8

U6 FLASH_D9 37 DQ9

AB19 FLASH_D10 40 DQ10

AA18 FLASH_D11 42 DQ11

AB18 FLASH_D12 48 DQ12

Y13 FLASH_D13 50 DQ13

AA12 FLASH_D14 52 DQ14

AB12 FLASH_D15 54 DQ15

V13 FMC_PWR_GOOD_FLASH_RST_B 44 RST_B

R20 FLASH_WE_B 14 WE_B

P22 FLASH_OE_B 32 OE_B

P21 FLASH_CE_B 30 CE_B

T19 FLASH_ADV_B 46 ADV_B

T18 FLASH_WAIT 56 WAIT

Table 1-7: Linear Flash Connections (Cont’d)

U1 FPGA Pin Schematic Net Name

U25 BPI FLASH

Pin Number Pin Name