SP605 Hardware User Guide www.xilinx.com 49

UG526 (v1.1.1) February 1, 2010

Detailed Description

Mode DIP Switch SW1 (Active-High)

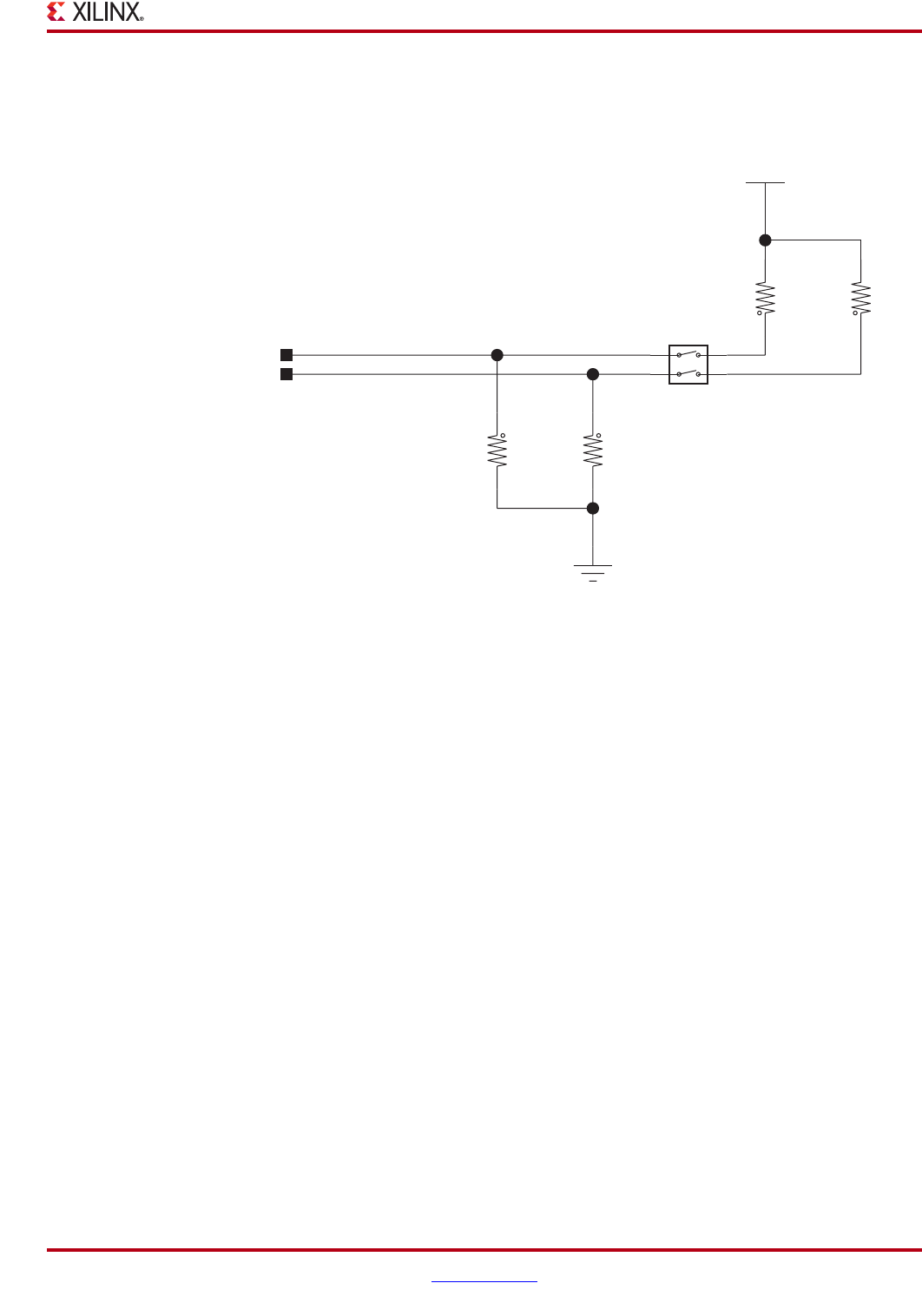

DIP switch SW1 sets the FPGA mode as shown in Figure 1-24 and Table 1-30, page 55.

References

For more information, refer to the Spartan-6 FPGA Configuration User Guide [Ref 2]. See

Table 1-30, page 55 for the configuration modes.

X-Ref Target - Figure 1-24

Figure 1-24: FPGA Mode DIP Switch SW1

VCC2V5

SDMX-2-X

1

2

R8

1.0K

1/10W

5%

1

2

R9

1.0K

1/10W

5%

1

2

4

3

SW1

1

2

5%

1/16W

200

R138

FPGA_M1

FPGA_M0_CMP_MISO

2

1

R139

200

1/16W

5%

UG526_24 _092409