114 MicroBlaze Development Kit Spartan-3E 1600 Edition User Guide

www.xilinx.com UG257 (v1.1) December 5, 2007

Chapter 14: 10/100 Ethernet Physical Layer Interface

R

The hardware evaluation versions of the Ethernet MAC cores operate for approximately

eight hours in silicon before timing out. To order the full version of the core, visit the Xilinx

website at:

http://www.xilinx.com/ipcenter/processor_central/processor_ip/10-100emac/

10-100emac_order_register.htm

UCF Location Constraints

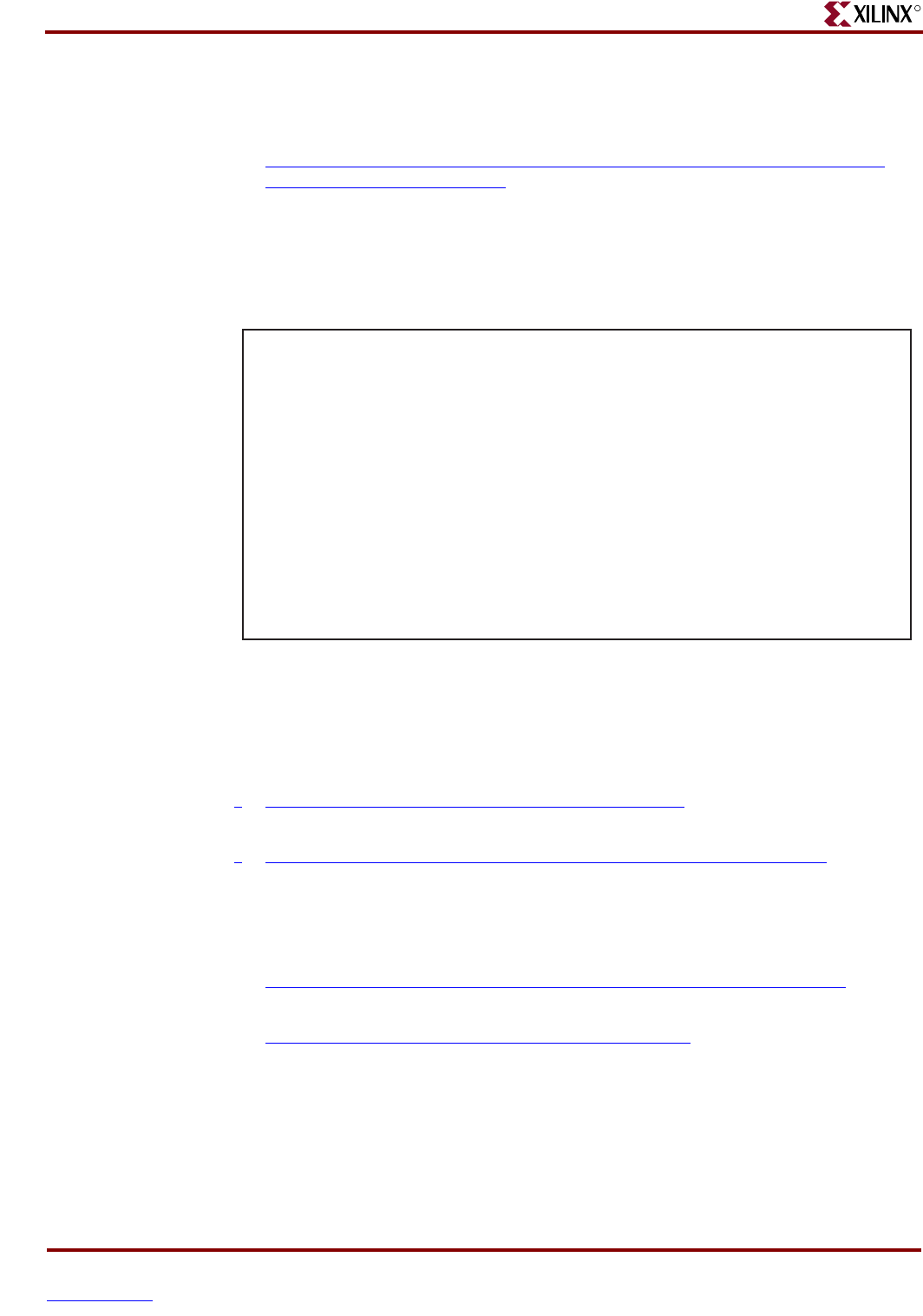

Figure 14-4 provides the UCF constraints for the 10/100 Ethernet PHY interface, including

the I/O pin assignment and the I/O standard used.

Related Resources

x Standard Microsystems SMSC LAN83C185 10/100 Ethernet PHY

x

http://www.smsc.com/main/catalog/lan83c185.html

x Xilinx OPB Ethernet Media Access Controller (EMAC) (v1.02a)

x

http://www.xilinx.com/bvdocs/ipcenter/data_sheet/opb_ethernet.pdf

x Xilinx OPB Ethernet Lite Media Access Controller (v1.01a)

x The Ethernet Lite MAC controller core uses fewer FPGA resources and is ideal for

applications the do not require support for interrupts, back-to-back data transfers,

and statistics counters.

x http://www.xilinx.com/bvdocs/ipcenter/data_sheet/opb_ethernetlite.pdf

x EDK 8.1i Documentation

x http://www.xilinx.com/ise/embedded/edk_docs.htm

Figure 14-4: UCF Location Constraints for 10/100 Ethernet PHY Inputs

NET "E_COL" LOC = "U6" | IOSTANDARD = LVCMOS33 ;

NET "E_CRS" LOC = "U13" | IOSTANDARD = LVCMOS33 ;

NET "E_MDC" LOC = "P9" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_MDIO" LOC = "U5" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_RX_CLK" LOC = "V3" | IOSTANDARD = LVCMOS33 ;

NET "E_RX_DV" LOC = "V2" | IOSTANDARD = LVCMOS33 ;

NET "E_RXD<0>" LOC = "V8" | IOSTANDARD = LVCMOS33 ;

NET "E_RXD<1>" LOC = "T11" | IOSTANDARD = LVCMOS33 ;

NET "E_RXD<2>" LOC = "U11" | IOSTANDARD = LVCMOS33 ;

NET "E_RXD<3>" LOC = "V14" | IOSTANDARD = LVCMOS33 ;

NET "E_RXD<4>" LOC = "U14" | IOSTANDARD = LVCMOS33 ;

NET "E_TX_CLK" LOC = "T7" | IOSTANDARD = LVCMOS33 ;

NET "E_TX_EN" LOC = "P15" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_TXD<0>" LOC = "R11" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_TXD<1>" LOC = "T15" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_TXD<2>" LOC = "R5" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_TXD<3>" LOC = "T5" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

NET "E_TXD<4>" LOC = "R6" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

UG257_14_04_060806