188

32-bit FR Family

■

FR Family Features

• CPU core capable of running at a peak rate of 64 VAX MIPS (CPU core performance) at 50 MHz while featuring

its compactness equivalent to 16-bit microcontrollers

• 5-stage pipelining and harvard-bus architecture, allowing efficient execution

• Implementation of, basically, 16-bit fixed length commands, providing high object code efficiency

• The command group enhanced for controllers and an algorithm engine, resulting in faster execution of instruc-

tions

• A variety of resources including the sum-of-product units

• Many kinds of internal peripheral devices

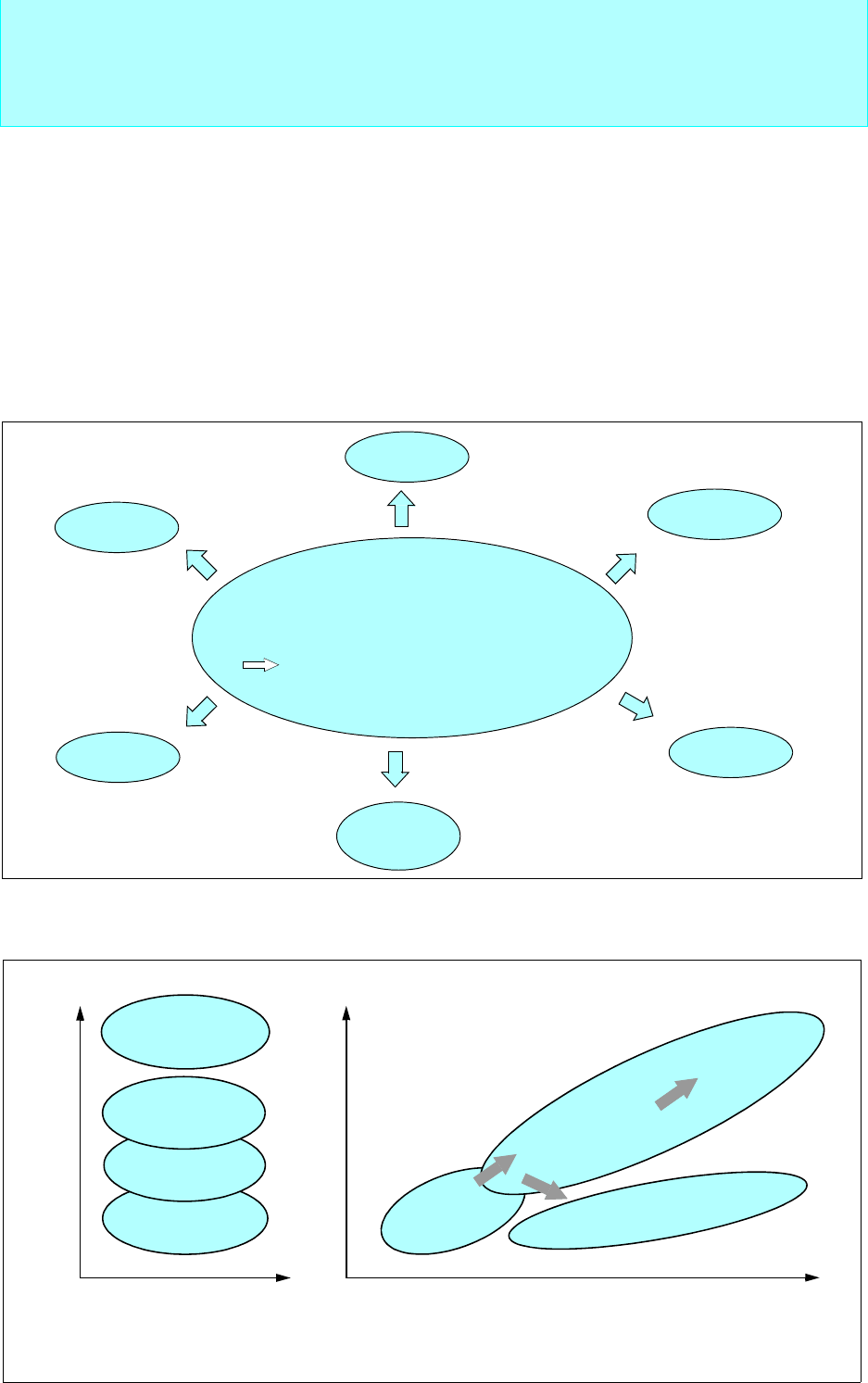

• FR architecture features

• Fujitsu embedded RISC controller

The FR family is designed for optimum use in control systems while the SPARClite is suitable for data

processing systems.

Fast interrupt

Real time processing

Algorithm engine

Special

Assembler

Efficient

Support for

Fixed-length

I/O operation

High coding

High-speed

RISC CPU features

• 5-stage pipelining

• 1 instruction/cycle

• Load/store

result in a compact CPU core.

60,000 transistors (including a multiplier & barrel shifter)

processing

processing

efficiency

instructions

high-level

languages

development

coding

(high-speed)

processing

F

2

MC: Single chip 8 to 16-bit microcontrollers

FR: Single chip-oriented (32-bit) RISC machines

SPARClite: Oriented for performance-focused open software

Performance

FR-V family

F

2

MC-16LX family

F

2

MC-8L family

FR family

Performance

FR30

Low power

Improvement in a bus

function

FR-Next

FR60 (66 MHz)

FR60Lite (33 MHz)