97

• Reduced power dissipation (5 V compatible products)

• Noise protection

Adoptation of multiplier circuit

Circuit optimization

Built-in noise filters for all pins

• Bus control

Bus sizing function: 8-bit or 16-bit bus width selectable

Software switching between non-multibus and multibus (device)

Supporting 8 ch. chip select (device)

• Built-in extended intelligent I/O service function (simple DMA function)

• Program patch processing function

Avoiding bugs by applying patches on a masked ROM

• Addition of signed multiplication and division instruction

• High-speed interrupt transition

High-speed transition achieved at the time of multiple interrupts

Expansion achieved to low-voltage and high-speed operation

5.0 V: Minimum machine clock of 62.5 ns/16 MHz

2.2 V: Minimum machine clock of 100 ns/10 MHz

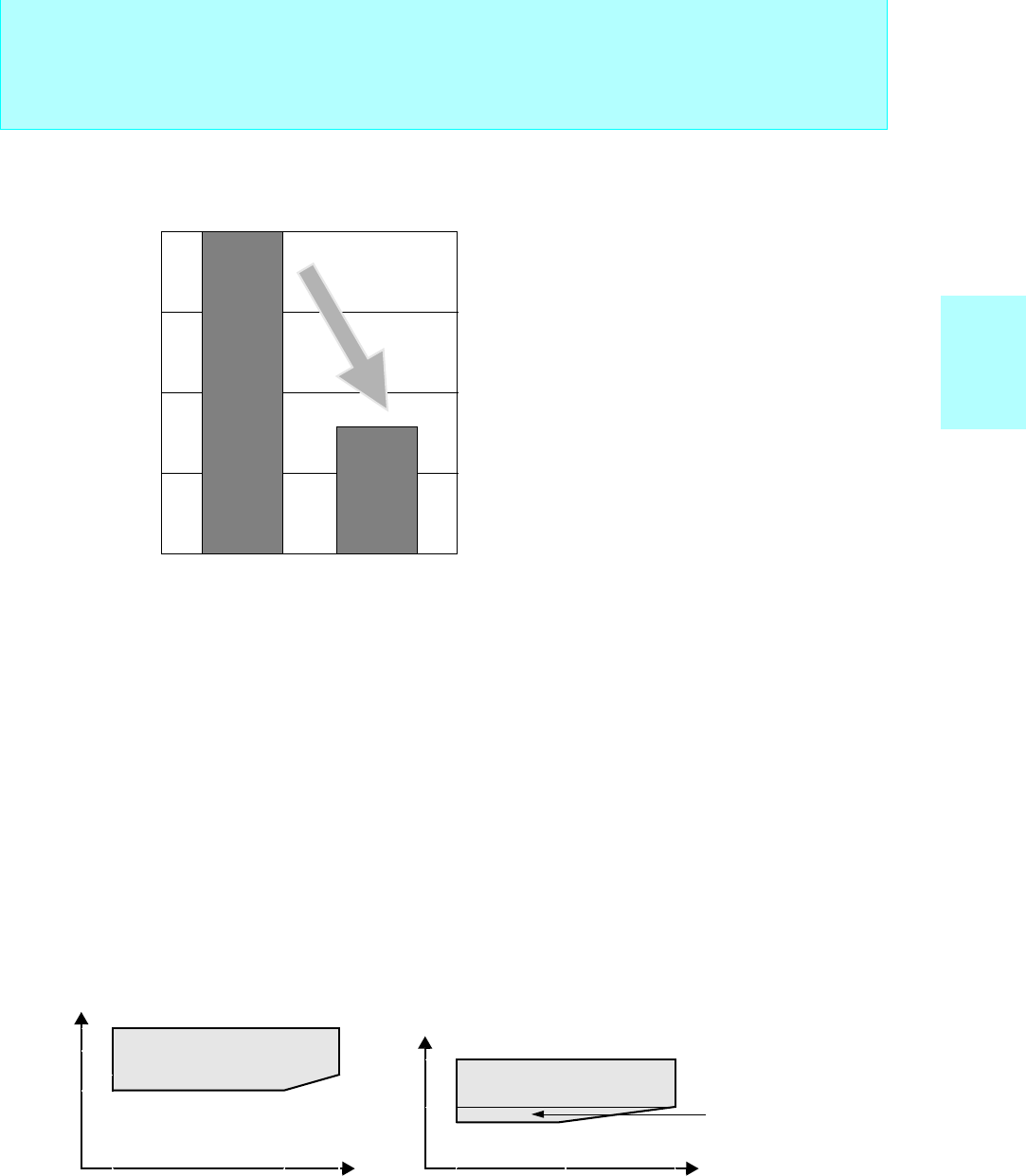

100%

75

50

25

0

FMC-16L FMC-16LX

Operating voltage

5 V version device

Internal operating frequency

1MHz 12MHz 16MHz

3 V version device

Internal operating frequency

1MHz 5MHz 10MHz

5.5V

4.5V

3.3V

3.0V

3.6V

1.8V

2.5V

2.2V

Operating voltage

Applicable according to

operating conditions

16-bit Proprietary F

2

MC-16LX Family

Features

F

2

MC-16LX Family