26 IBM System p5 520 and 520Q Technical Overview and Introduction

2.1 The POWER5+ processor

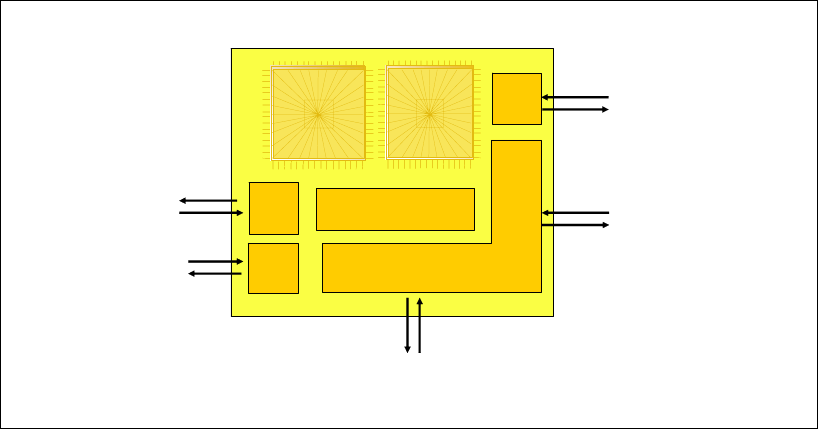

The IBM POWER5+ processor capitalizes on all the enhancements brought by the POWER5

processor. For a detailed description of the POWER5 processor, refer to IBM System p5 520

Technical Overview and Introduction, REDP-9111. Figure 2-2 shows a high level view of the

POWER5+ processor.

Figure 2-2 Power5+ processor

The CMOS10S technology in the POWER5+ processor uses a 90 nanometer or nm

fabrication process, which enables:

Performance gains through faster clock rates

Processor size reduction (243 mm compared with 389 mm)

The POWER5+ processor is 37% smaller than the POWER5 processor. It consumes less

power and requires less cooling. Thus, you can use the POWER5+ processor in servers

where previously you could only use lower frequency processors due to cooling restrictions.

The POWER5+ design provides the following additional enhancements:

New page sizes in ERAT and TLB. Two new pages sizes (64 KB and 16 GB), which were

recently added in PowerPC® architecture.

New segment size in SLB. One new segment size (1 TB) was recently added in PowerPC

architecture.

The TLB size has been doubled in the POWER5+ over the POWER5 processors. The

TLB in POWER5+ has 2048 entries.

Floating-point round to integer instructions. New instructions (frfin, frfiz, frfip, frfim) have

been added to round floating-point numbers with the following rounding modes: nearest,

zero, integer plus, and integer minus.

Improved floating-point performance.

Lock performance enhancement.

Enhanced SLB read.

True Little-Endian mode. Support for the True Little-Endian mode as defined in the

PowerPC architecture.

Core

2.1 GHz

Core

2.1 GHz

Core

2.1 GHz

Core

2.1 GHz

1.9 MB L2

L3

Intf

Mem

Cntrl

GX+

Intf

SMP

Fabric

Bus

L3

Bus

Mem

Bus

GX+

Bus

Vertical

Fabric

Bus

POWER 5+ Processor

Enhanced Distributed Switch

(Fabric Bus Controller)