32 IBM System p5 520 and 520Q Technical Overview and Introduction

To determine how much memory is installed in a system, use the following command:

# lsattr -El sys0 | grep realmem

realmem 524288 Amount of usable physical memory in Kbytes False

2.3.2 OEM memory

OEM memory is not supported or certified by IBM for use in an IBM System p5 server. If the

server is populated with OEM memory, you could experience unexpected and unpredictable

behavior, especially when the system is using Micro-Partitioning technology.

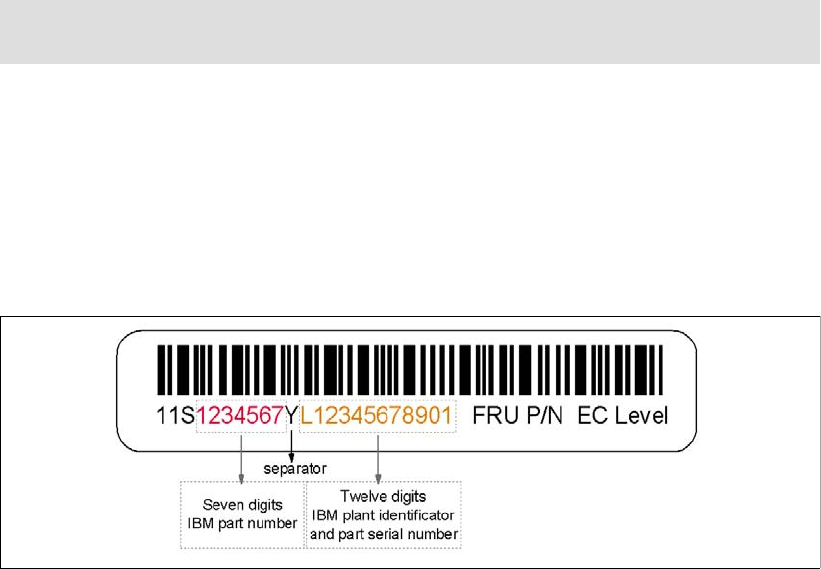

All IBM memory is identified by an IBM logo and a white label that is printed with a barcode

and an alphanumeric string, as illustrated in Figure 2-8.

Figure 2-8 IBM memory certification label

2.3.3 Memory throughput

The memory subsystem throughput is based on the speed of the memory. An elastic

interface, contained in the POWER5+ processor, buffers reads and writes to and from

memory and the processor. There are two Synchronous Memory Interface (SMI-II) chips,

each with a single 8-byte read and 2-byte write high speed Elastic Interface-II bus to the

memory controller of the processor. The bus allows double reads or writes per clock cycle.

Because the bus operates at 1066 MHz, the peak processor-to-memory throughput for read

is (8 x 2 x 1056) = 16896 MBps or 16.89 GBps. The peak processor-to-memory throughput

for write is (2 x 2 x 1056) = 4224 MBps or 4.22 GBps, making a total of 21.12 GBps.

The 533 MHz DDR2 memory DIMMS operate at 528 MHz through four 8-byte paths. Read

and write operations share these paths. There must be at least four DIMMs installed to

effectively use each path. In this case, the throughput between the SMI-II and the DIMMs is

(8 x 4 x 528) or 16.89 GBps.

These values are maximum theoretical throughputs for comparison purposes only. Table 2-3

provides the theoretical throughput values for different configurations.

Note: A quad must consist of a single feature (that is, be made of identical DIMMs). Mixed

DIMM capacities in a quad will result in reduced RAS.