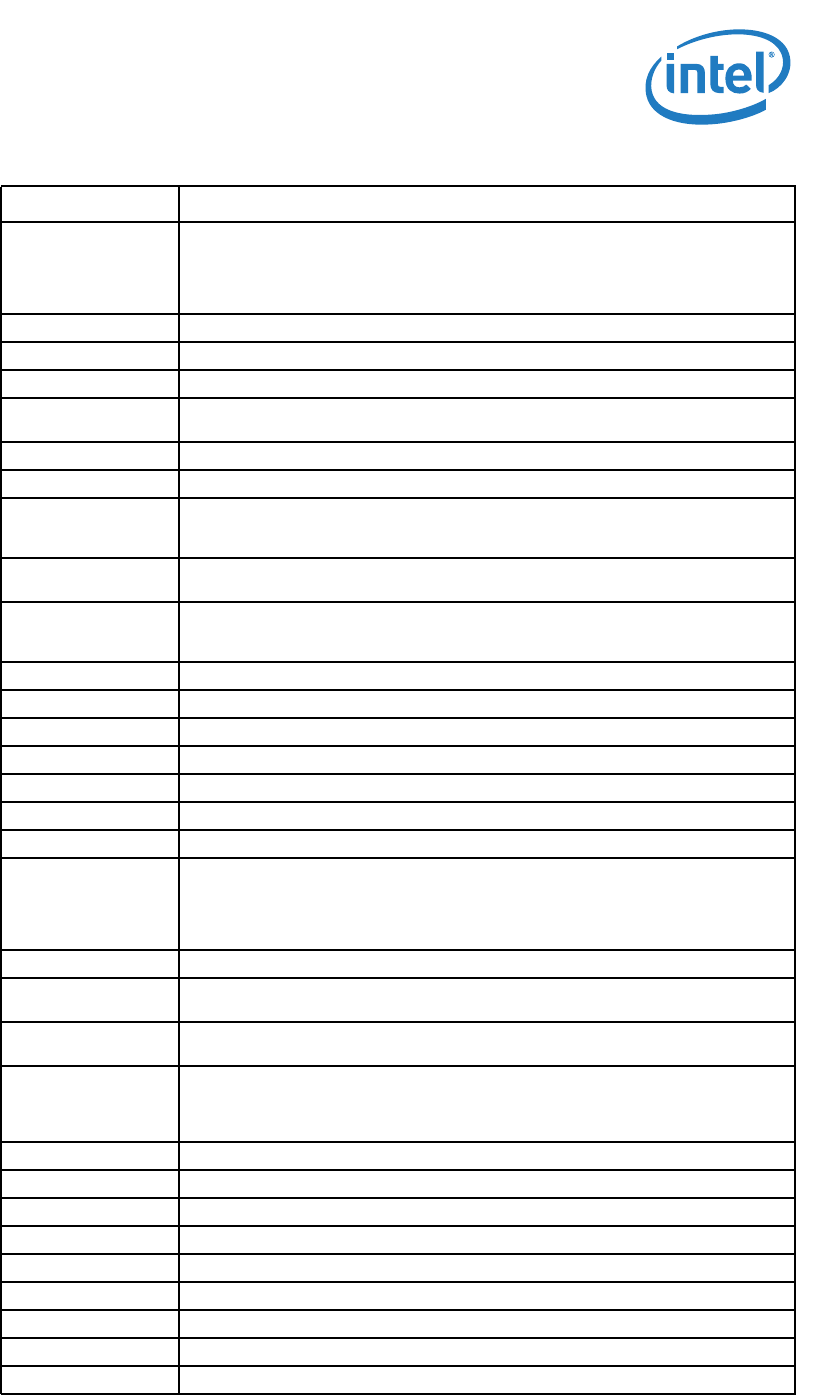

Datasheet 15

Introduction

Intel

®

VT-d

Intel

®

Virtualization Technology (Intel

®

VT) for Directed I/O. Intel VT-d is a hardware

assist, under system software (Virtual Machine Manager or operating system)

control, for enabling I/O device virtualization. Intel VT-d also brings robust security

by providing protection from errant DMAs by using DMA remapping, a key feature of

Intel VT-d.

IOV I/O Virtualization

Jitter Any timing variation of a transition edge or edges from the defined Unit Interval (UI).

JTAG Joint Test Action Group

LGA2011-0 Socket

The LGA2011-0 land FCLGA package mates with the system board through this

surface mount, LGA2011-0 contact socket.

LLC Last Level Cache

MCH Memory Controller Hub

NCTF

Non-Critical to Function: NCTF locations are typically redundant ground or non-

critical reserved; thus, the loss of the solder joint continuity at end of life conditions

will not affect the overall product functionality.

NEBS

Network Equipment Building System. NEBS is the most common set of environmental

design guidelines applied to telecommunications equipment in the United States.

PCH

Platform Controller Hub. The next generation chipset with centralized platform

capabilities including the main I/O interfaces along with display connectivity, audio

features, power management, manageability, security, and storage features.

PCI Express* PCI Express* Generation 2.0/3.0

PCI Express* 2 PCI Express* Generation 2.0

PCI Express* 3 PCI Express* Generation 3.0

PCU Power Control Unit

PECI Platform Environment Control Interface

PLE Pause Loop Exiting

Processor The 64-bit, single-core or multi-core component (package)

Processor Core

The term “processor core” refers to silicon die itself that can contain multiple

execution cores. Each execution core has an instruction cache, data cache, and

256-KB L2 cache. All execution cores share the L3 cache. All DC and AC timing and

signal integrity specifications are measured at the processor die (pads), unless

otherwise noted.

QoS Quality of Service

Rank

A unit of DRAM corresponding four to eight devices in parallel. These devices are

usually, but not always, mounted on a single side of a DDR3 DIMM.

SCI

System Control Interrupt. Used in Advanced Configuration and Power Interface

(ACPI) protocol.

SMBus

System Management Bus. A two-wire interface through which simple system and

power management related devices can communicate with the rest of the system. It

is based on the principals of the operation of the I

2

C* two-wire serial bus from

Philips* Semiconductor.

SSE Intel

®

Streaming SIMD Extensions (Intel

®

SSE)

STD Suspend-to-Disk

STR Suspend-to-RAM

SVID Serial Voltage Identification

TAC Thermal Averaging Constant

TAP Test Access Port

TCC Thermal Control Circuit

TDP Thermal Design Power

TLP Transaction Layer Packet

Table 1-1. Terminology (Sheet 2 of 3)

Term Description